1. 칩 인터커넥션

: 1차적으로 침에서 외부로 연결되는 기술.

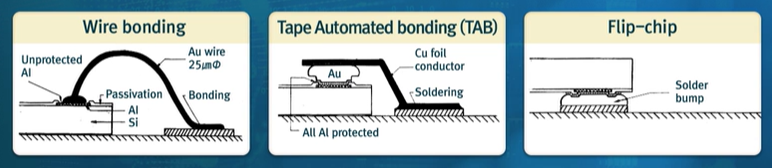

- 와이어본딩 - 테잎 오토매이티드 본딩 - 플립칩 본딩

- 와이어본딩.

: 칩의 인풋 아웃풋 패드, 입풀력패드, 리드프래임 등을 머리카락ㅂ다 얇은 와이어로 연결.

- 열압착. Tehrmocompression 본딩. (초창기 사용)

캐필러리를 통해 공급되는 금 와이어의 끝을 볼 형태로 둥글게 만든 후 칩의 패드에 본딩함.

그다음 캐필러리를 이용하여 와이어를 리드프래임이나 기판 패드로 이동시킨 후 다시 본딩함.

마지막으로 와이어를 끊어주면 완성.

- 열압착에서는 열과 압력만드로 본딩하여 공정 온도가 높음 (고분자재료 손상 가능성)

현재는 사용하지 않음

2) 울트라소닉 본딩 (초음파 본딩) Wedge 본딩이라고도 함.

초음파 진동을 가하면서 압착, 상온에서 본딩하는 방법.

본딩와이어로 알루미늄을 사용하고 AL표면 산화층은 초음파 진동을 가해 파괴 가능.

(알루미늄 표면에는 자연산화층이 존재)

초음파 방식은 웻지 방식이 방향성을 가지는 방식이므로 생산성이 떨어지고 자입 가격이 비싸서 특수 용도로만 사용되는 방법.

3) Thermosinic 본딩 (T/S 열초음파 본딩)

본딩 과정은 열압착 방식과 비슷함. 그러나 초음파 에너지를 가해 본딩함. -> 공정 온도를 150도정도로 낮출 수 있음

(요즘 산업계에서 가장 많이 사용되는 방법) + 속도 빠름.

와이어본딩 장점.

-가장 광범위하게 사용되는 방식이다.

1. 경제적이며 생산성이 우수함.

:웨이퍼상에서의 추가 공정이 없음. 적은 공정비용 및 저렴한 장비 가격.

본딩 장비 기술의 발전으로 장비 가격도 싸지고 속도는 빨라짐.

2. 높은 적응성과 공정 신뢰성

: 칩의 모양이 바뀌어도 소프트웨어를 이용해 패드 위치를 이용하여 조절하기 용이.

적응성이 좋고 공정 수율이 거의 100퍼

와이어 본딩을 지원하는 기반기술이 많이 있음.

단점

1. 입출력패드의 제한적 개수.

: 칩이 발달함ㄴ에 따라 I/O 패드가 수백개 이상인 칩에서는 적용 불가, 와이어 본딩을 하기 위해서는 캐필러리같은 공정 툴이 필요함.

패드피치가 큰 경우에는 패드 사이의 거리가 넓어서 문제 안되나. 미세화에따라 피치가 줄어듦. 그러나 캐필러리의 크기 떄문에 줄이는데 한계가 있음.

-> 캐필러리를 홀쭉하게 하기에도 한계, 어긋날 2열 배치를 하더라도 와이어 사이의 접촉문제가 발생할 수 있음.

패드 밀도가 높은 곳에서는 적용하기가 어려워짐.

2. 칩에서 외부로의 배선이 길어 전기적 성능 저하.

: 고속도 칩에는 부적합 (전선이 길어 단점)

+ 금가격 폭등

-> 구리 와이어를 사용하는 방식이 고안됨. 금에 비해서 재료가격이 금에 비해 매우 저렴하고 전기전도도와 열 전도도가 더 우수하고, 구리의 기계적 강도가 더 우수하여 몰드 스윕에 대한 저항이 더 큼.

그러나, 구리 와이어를 사용할때의 단점은. 금에 비해서 산화, 부식에 취약함, 구리 와이어 사용할 떄 구리가 산화되면 안되므로, 구리 산화를 막을 수 있도록 특별한 장비가 필요. 또한 패키지 밀봉이 안될 경우에도 부식이 진행되므로 밀봉이 중요함. 또한 경도가 더 크므로 접합부에 가해지는 압력이 강해 Cratering이 발생할 수 있음. -> 접합 인자를 정밀하게 조절해야 함.

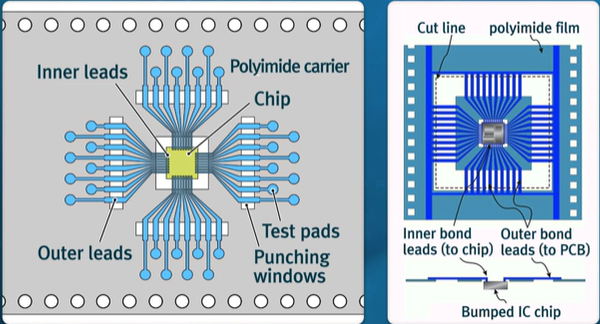

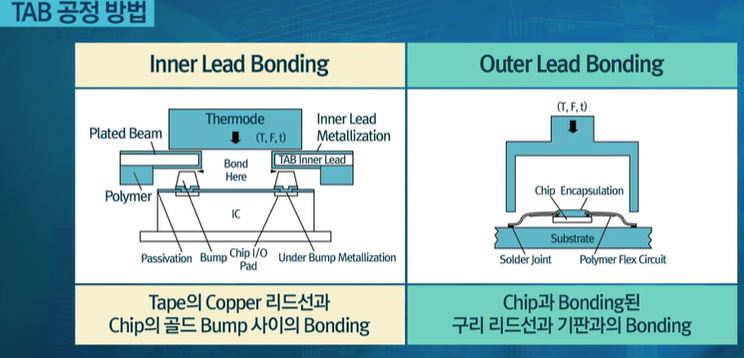

- Tap Automated Bonding (TAB)

두 본딩 모두 온도와 압력을 가해 모든 리드를 한꺼번에 접합.

특징 )

1. 일괄 본딩 가능.

:와이어본딩에서는 하나하나 했지만. 이 방법은 칩의 모든 패드와 와이어를 한꺼번에 가능. -> gang 본딩.

2.미세 패드피치나 I/O 수가 많은경우도 가능

: 캐필러리 같은 본딩 툴이 필요하지 않음.

3. 패키지 두꼐 감소 가능

: 와이어 본딩은 루프가 형성되어 두꼐가 증가. 따라서 얇아야 하는 IC카드나 평판 디스플레이용으로 사용됨.

이러한 TAB은 와이어 본딩 속도 개선을 위해 개발됐는데.

- 구리 미세 회로가 형성된 테잎, 본딩을 위해 칩에 금속 범프가 추가로 필요하고. 접합 공정에서 제한적으로 사용 (공정 안정성이 와이어본딩보다 떨어짐) (평판 디스플레이)

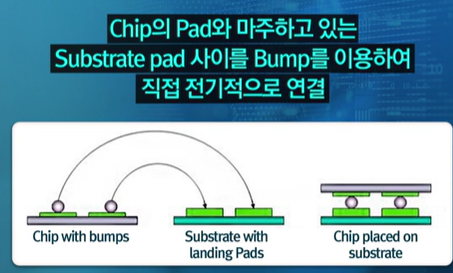

- Filp Chip 본딩.

칩의 패드와 마주하고 있는 기판 패드 사이를 범프를 이용하여 직접 전기적으로 연결.

앞의 두 방법과 달리 칩의 소자가 있는 면과 기판 패드가 있는면이 서로 마주봄.

범프 재료로 주로 Solder를 사용.

초기에는 납 주석 솔더 혹은 합금을 사용하지만 납의 유해성때문에 바뀜.

주로 주석에 은이 조량 있는 합금을 사용함.

특수한 경우에는 인이나 금 주석 솔더도 사용함.

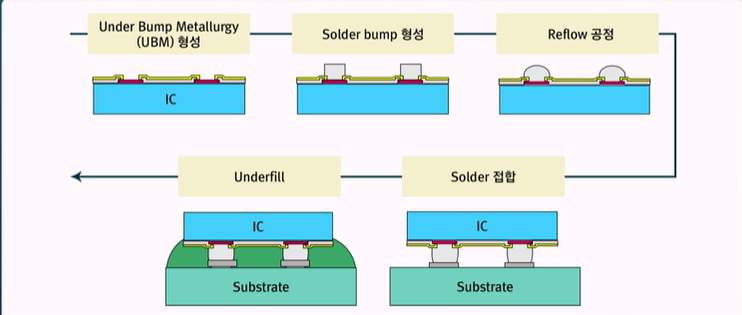

공정순서.

: UBM 이란 솔더의 젖음성을 향상시켜 더 솔더링이 잘 되기 위해 칩의 패드 위에 다층으로 구성된 금속층을 말함

장점

1. I/O 패드 밀도 증가 가능.

: 앞의 두 방법과 칩의 크기가 같더라도 더 많은 수의 패드를 생성 가능.

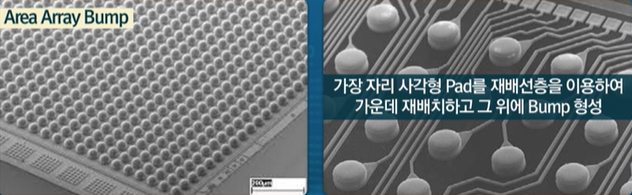

-> 와이어 본딩이나 탭방법은 아이오패드의 칩의 가장자리에 있어야 하지만. 플립칩은 칩의 모든 면적에 입출력 패드를 만들 수 있음. 기존의 가장자리에 있는 패드를 재분배하여 칩의 전면에 바둑판 모양으로 재배치를 가능하게 함. (Are array)

전체 면적의 범프를 재배치하여 피치가 넓으면서도 패드 크기 또한 원래 패드 크기보다 더 큰 범프를 제조할 수 잇음.

핀수가 많은 칩의 본딩 방법으로 플립칩 기술이 가장 최적화됨.

2. 고밀도 칩 패키징.

:같은 기판 면적에 더 많은 수의 칩을 올릴 수 있음.

-앞선 방법들은 칩을 기판과 연결하기 위해서는 칩보다 더 큰 면적이 필요하지만. 플립칩은 범프로 연결되므로 칩의 크기만큼의 면적을 이용하여 바로 인접해서 칩을 연결시킬 수 있음.

즉 칩 접합에 필요한 유효 점유 면적이 작아 더 고밀도의 칩을 생성 가능.

3. 짧은 배선 길이

: 오이어 본딩은 ㅇ본딩 루프떄문에 배선이 길어짐. TAB은 그나마 짧아도 플립칩보다는 훨씬 김. 그러나 플립칩은 범프로 연결되므로 배선이 매우 짧음.

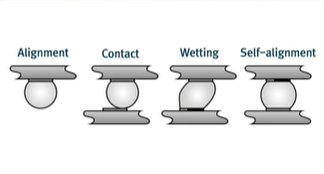

4. 자가정렬 (Self Alignment)

: 정렬할 떄 약간의 뒤틀림이 있더라도 경화되면서 알아서 정렬이 가능함 (수율 향상)

5. 언더필 공정 적용 시 신뢰도 향상.

단점.

1. 높은 제조 비용

: 범프 재배치 설꼐 비용과 범프 형성 공정 비용등이 추가되어야 함.

2. 본딩 후 광학적 검사 불가능

: 실리콘이 가시광선을 투과시키지 못하므로. 본딩 이후 광학적 검사가 불가능

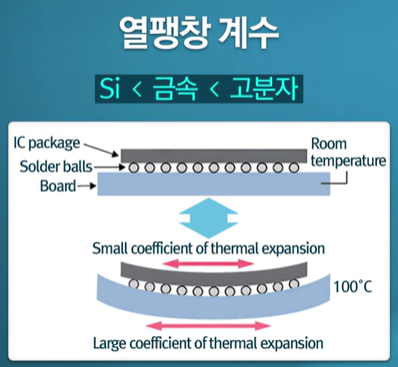

3. 열 피로에 의한 솔더 접합부 파손 가능.

: 사용 도중 온도 변화가 생기면 열 피로에 의해 솔더 접합부 파손 가능.

열팽창 계수 : SI < 금속 < 고분자

-> 주로 고분자로 생성되어 있는 소자라면 더 많이 휘어짐. (열팽창 계수가 서로 다른것이 문제)

식으면 다시 원래의 모습으로 돌아오지만. 이 과정이 많아지면 열피로에 의해 소자 내부가 깨질수 있음. (균열 성장)

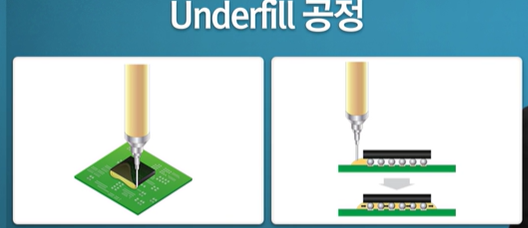

* Under fill 공정.

에폭시가 주재료인 액상 접착제를 도포하여 칩과 기판 사이를 채우는 방식. 모세관 현상에 의해 액상 접착제가 칩과 기판 사이의 틈으로 들어감.

범프가 접착제로 둘러싸여 외부의 충경이나 환경 변화로부터 보호 가능.

언더필 공정을 적용하면 열 사이클에 따른 신뢰성이 엄청나게 상승.

온도 증가에 따른 팽창 차이 억제.)

*

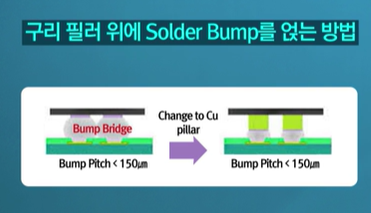

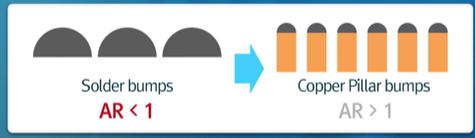

미세 피치에서 솔더 범프 제작 문제점.

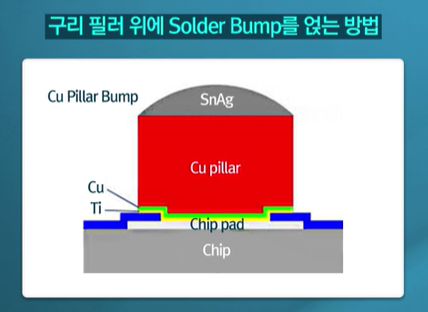

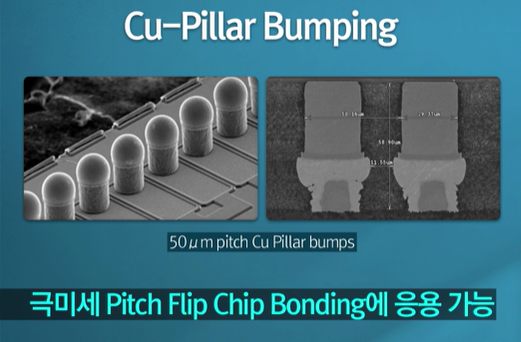

인접 범퍼 사이에 접촉이 발생할 수 있음. 이에따라 솔더 범퍼대신 구리 필러위에 솔더 범프를 얹는 방법을 개발.

장점.

솔더 범퍼는 종횡비가 1이하지만. 카파 필라 범프는 종횡비가 1을 넘기 떄문에 여러가지 장점 발생.

같은 패드피치에서 범프 사이의 간격이 넓어 언더필로 범프 사이를 채우는것도 쉽고 인접 범프 사이 접촉 감소, 또 피치의 크기감소(20마이크로 이하피치에서도 본딩 가능)를 이룰 수 있게 함. 또 범프가 주로 구리로 이루어지므로 전기 전도 도 우수하고 일렉트로 마이그레이션의 저항성도 큼.

- 리드프래임을 사용하지 않는 패키징 3가지

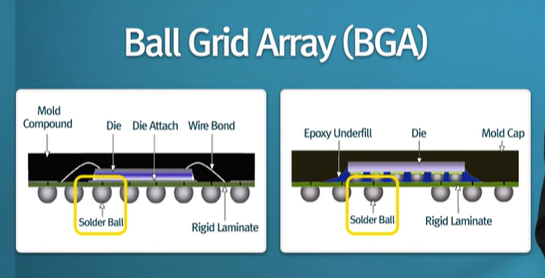

- Ball Grid Array (BGA)

패키지 옆으로 리드가 나와있지 않고 패키지 밑면에 작은 솔더 볼들이 붙어있음. 칩과 기판의 연결은 와이어본딩이나 플립칩을 이용함.

특징.

1. 표면 실장용 IC 패키지.

:패키지 밑에 있는 솔더 볼을 패드와 정렬시켜 솔더 리플로우 방식으로 접합.

2. Area array 패키지

: 플립칭에서와 같이 패키지 밑면 전체에 IO 패드가 있는 방식.

3. 주로 솔더 볼을 통해 다음 단계 이용

: 반도체 패키지와 그 다음 단계를 주로 솔더 볼을 이용함.

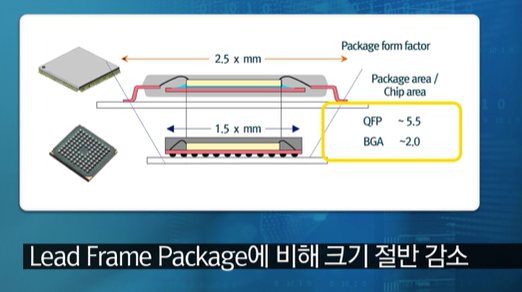

-> 크기를 반 이하로 줄일 수 있음. 전자기기의 크기 감소에 가장 크게 영향을 미침.

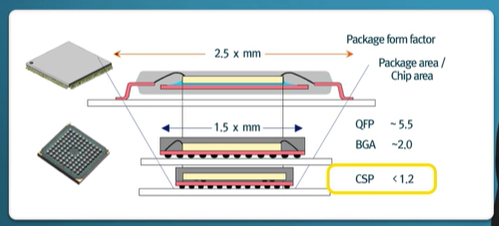

- Chip Scale Package (CSP)

패키지 크기가 칩 크기의 120퍼를 넘지 않을 떄 사용됨.

특징.

1. 기존 패키지보다 더 작고 더 얇으며 가벼움.

2. 작은크기, 짧은 배선길이, 우수한 전기적 성능

리드프레임과 비교해서 5배, BGA에 비해서는 2배이상 작음.

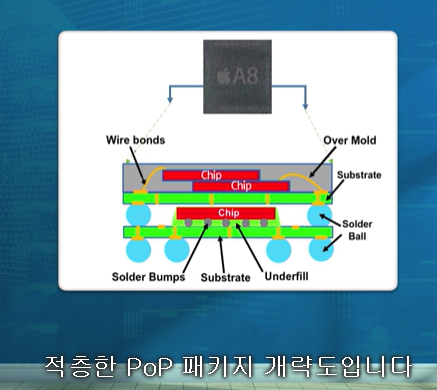

- Package on Package (POP)

패키지 위에 별개의 패키지를 쌓는 방식으로 서로 연결된 패키지.

예시 : BGA 칩 두개 쌓음

장점 :

1. 패키지 점유 면적 감소되어 PCB 크기 감소.

2. 기존 표면 실장 방법 이용하여 추가적 기반 시설 불필요.

3.독립된 패키지 사이의 접합이므로 다양한 기능을 혼합 가능

4. 신뢰성이 확보된 개별 칩의 적층이므로 신뢰성 문제에도 강함.

POP의 개발로 전자제품 시스템의 두꼐와 무게 감소 (큰 비용 x)

'반도체 공정 > Packaging (패키징 후공정)' 카테고리의 다른 글

| 패키징 기초 (0) | 2022.03.08 |

|---|