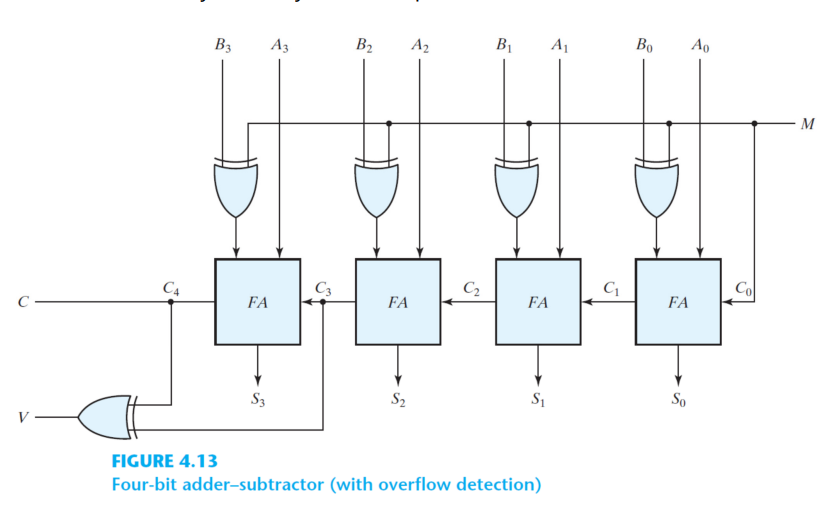

4-5. 2진 감산기 (Binary subtractor)

지금까지 알아본 가산기(adder)을 이용해서 감산기(subtractor)을 만들 수 있다.

컴퓨터는 빼기의 연산을 하더라도 보수의 개념을 이용해서 뺄셈을 수행하기 때문에 같은 하드웨어로 사용 가능하다.

자 위의 그림에서 입력단에 사용된 싱글인풋 XOR gate를 보자 (실제로는 M과 입력단 두개의 입력)

감산기가 앞서 배운 가산기와 달라진 점이라면 앞에 XOR 게이트 하나가 붙어있다는 것 밖에는 없다.

XOR의 연산을 차근차근 따라가 보면 XOR의 쓰임새에 대해서 알 수 있다.

경우의 수는 M이 0이거나 1인 경우만 존재하기 때문에. 두가지 경우를 생각해 보겠다.

M = 0으로 고정된 경우

XOR연산은 두 입력 모두 0이거나 1인 경우만 0을 출력하고 하나라도 1이 입력될 경우 1을 출력하기 때문에

입력이 0이 들어오면 (0 0)의 경우로 0을 출력, 입력이 1이 들어오면 (0 1)의 경우로 1을 출력

버퍼의 역할과 같이 입력 신호를 그대로 전달

M = 1으로 고정된 경우

입력이 0이 들어오면 (1 0)의 경우로 1을 출력, 입력이 1이 들어오면 (1 1)의 경우로 0을 출력

인버터의 역할과 같이 입력 신호를 보수화 해서 전달

즉. M이 XOR gate를 버퍼로 사용하게 할 수도, 인버터로 사용하게 할 수도 있게 하는 입력인 것이다.

따라서 보수의 뺄셈의 연산을 위해 2진 보수를 구하는 과정과 동일한 인버터의 역할을 하도록 M=1로 고정한다.

그 이후 가산기의 역할과 같이 덧셈을 수행해주면 보수를 이용한 뺄셈의 과정이 나타나는 것이다.

4-6. 2진 곱셈기 Binary multiplier

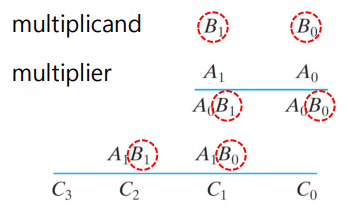

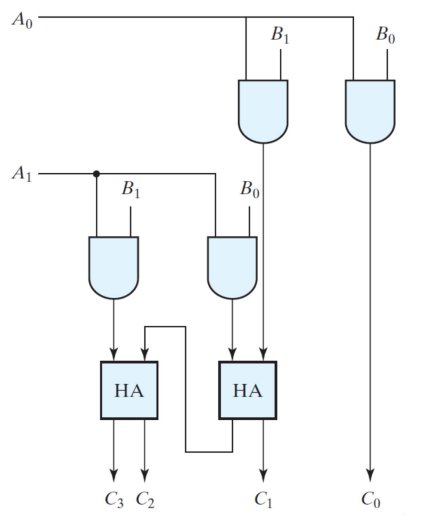

B1 과 B0로 이루어진 2bit 2진수를 다른 2bit 2진수 A1 , A0를 곱하는 과정을 살펴보자면.

곱셈의 과정을 논리연산적으로 생각해 보자면. 각 자리에 있는 수끼리 AND의 연산을 하고, 한 자릿수를 왼쪽으로 옮겨 연산되지 않은 입력끼리 AND연산을 해 주어 서로 더해주는 과정이다.

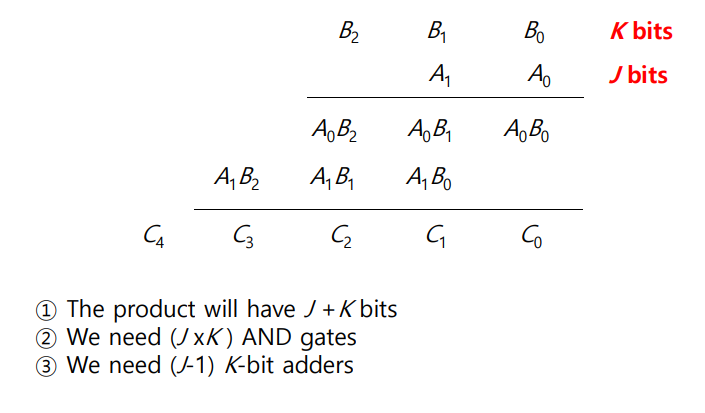

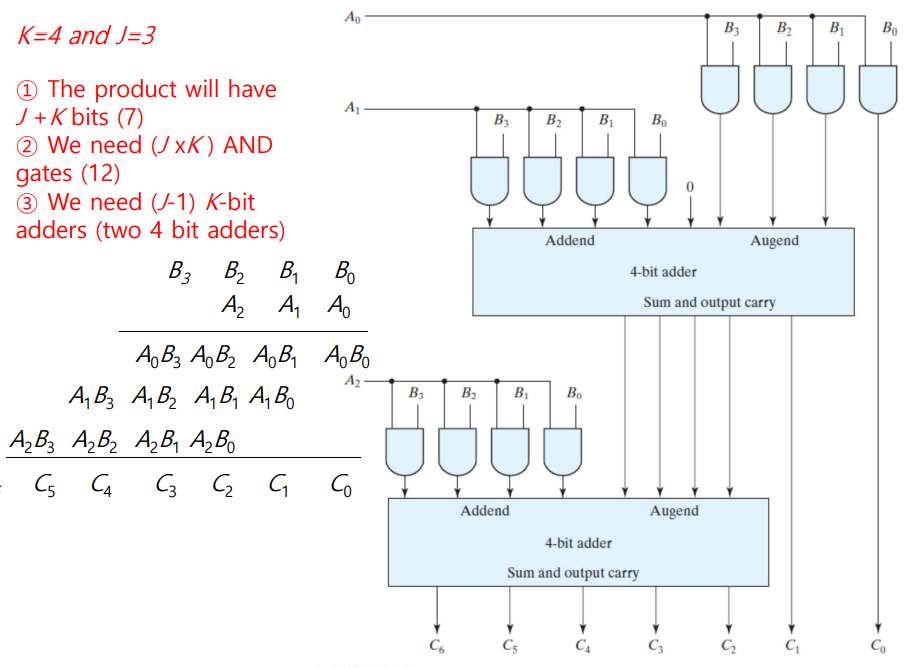

곱셈기를 설계하기 위해서 K bit을 가진 수에 J bit을 가진 수를 곱하게 된다면.

결과적으로 J x K의 개수만큼 AND gate가 필요하고 J + K bit의 곱을 만들기 위해 J-1 만큼의 K 비트 가산기가 필요하다.

예시로 K = 4 bit, J = 3 bit를 가진 2진수의 곱셈의 과정을 보자.

'디지털공학 > Chap 4.' 카테고리의 다른 글

| Chap 4. 조합 논리 (1) . Combinational Logic (0) | 2022.01.13 |

|---|