728x90

UART (Universal Asynchronous Receiver Transmitter)

→ 범용 비동기화 송수신기

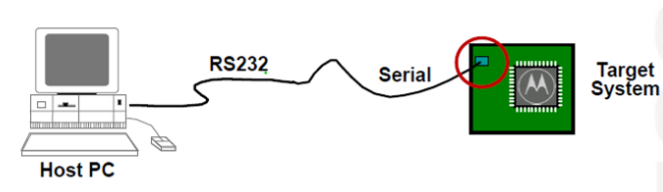

FPGA 동작 검증 환경

- FPGA에 입출력을 넣어 사용할 수 있는 방법은 여러가지.

- 이때 HOST PC를 통한 값의 입력 및 출력을 FPGA로 사용하고자 할때 UART 통신이 매우 General 하게 사용됨.

→ 병렬 데이터의 형태를 직렬 방식으로 전환하여 데이터를 전송하는 컴퓨터 하드웨어의 일종.

→ 통신 데이터는 메모리 또는 레지스터에 들어 있어 이것을 차례대로 읽어 직렬화 하여 통신.

(최대 8bit을 기본단위로 사용)

→ UART는 컴퓨터의 주변기기 일종으로 분류할 수 있는 개별 집적 회로

UART FRAME

- UART 통신의 기본 단위 (Packet 이라고도 함)

- 비동기 data 전송에서 start/stop bit 단위로 구분하여 연속된 data 구분.

- 보내지는 신호가 없을 경우 (ideal state) logical 1 유지.

- start bit : 통신 시작을 알림 (logical 0)

- data bit : 통신 data (5~9bit 크기)

- parity bit : 오류 검출 (None, Odd, Even)

- even (짝수) parity

- data의 각 비트의 1 개수가 홀수가 되면 1. (짝수는 0)

- odd (홀수) parity

- data의 각 비트의 1 개수가 짝수가 되면 1. (홀수는 0)

- stop bit (통신 종료 알림) : logical 1로 통신 종료를 알림. (1~2bit 크기 set)

https://m.blog.naver.com/ansdbtls4067/220886661657

패리티 비트(Parity Bit)란 무엇인가?

안녕하세요? 땜쓰 입니다. 이번 포스팅에서는 패리티 비트(Parity Bit)에 대해서 알아보는 시간을 갖도록...

blog.naver.com

4 asynchronous communication parameters.

- Baud rate(bps) : 9600bps

- 1초 당 프레임(packet)수

- 단위 : bit/s (bps)

- 수신부, 송신부의 baud rate의 동기화 필요

- 클럭 주파수를 바꿀 때마다 baud rate 계산 필요

- clock을 세는 방법으로 동기화 가능

https://velog.io/@lutein/Baud-Rate-BPS-UART

Baud Rate & BPS

UART에 필요한 개념

velog.io

- number of data bits : 8bits

- Parity bit : None(N)

- Number of stop bits : 1 bit

module 설계 기초.

728x90

'FPGA' 카테고리의 다른 글

| MIPI (Mobile Industry Processor Interface) - CSI, DSI, D-PHY, C-PHY (0) | 2024.06.19 |

|---|---|

| SPI Interface - FPGA to Chip (0) | 2024.06.12 |

| SPI Interface Basic Concept (0) | 2024.06.12 |