728x90

MIPI (Mobile industry Processor Interface)

모바일 Processor Interface 표준

Interface 유형

- Physical Layer

- Multimedia

- Chip-to-Chip / Inter-Processor Communications

- Device Control and Data Management

- System debugging

- Software Integration

→ 고대역폭 성능, 저전력, EMI 최소화 등에 대해 최적화.

Multimedia 범주

- Application Layer

- Protocol Layer

- PHY Layer

CSI (Cameral Serial Interface)

DSI (Display Serial Interface)

→ 카메라/디스플레이 모듈 간의 Interface

MIPI D-PHY

D-PHY (500Mbit/s)

Camera / Display Application

App.에 대한 고속, 저전력 통신 지원

Master – Slave 형태 (주 데이터 전송 방향 존재)

→ Master 에서 클럭 채널에 DDR 클럭 제공

→ Slave 에서 클럭 채널에서 클럭 신호 수신

구성

Clock Lane (단방향 M → S)

Data Lane (단/양방향 M ↔ S)

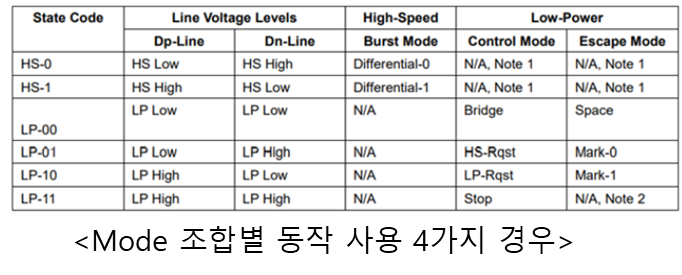

동작

HS(High Speed) mode, LP (Low Power) mode 2가지 존재

MIPI C-PHY

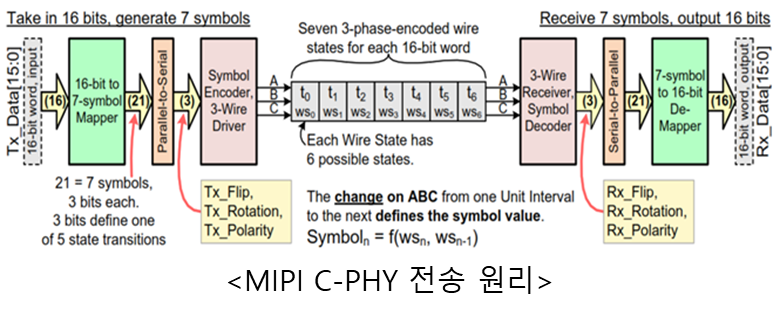

C-PHY

D-PHY와 동일하게 CSI, DSI 지원

D-PHY와 동일하게 Protocol 계층 통신 사용

전송 채널을 유연하게 선택 가능

구성

3개의 와이어로 구성

Master – Slave 구조

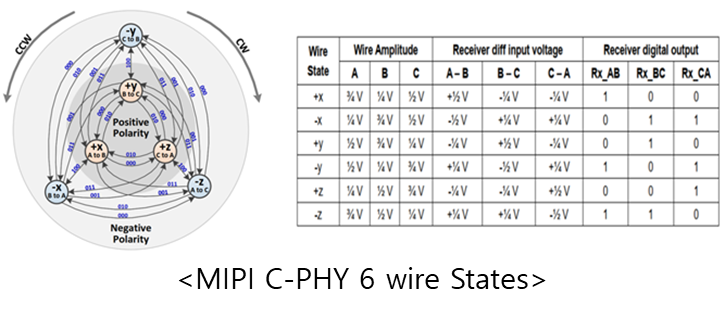

저전력 LP Mode, 고속 HS Mode 존재.

→ LP mode : interface 제어 신호 전송 or data

→ HS mode : tri-state data 전송

DSI

C/D-PHY는 MIPI App. 간 물리적 연결

Display or Camera 데이터 전송을 위해서는 추가적인 Protocol이 필요.

DSI (Display Serial Interface)

디스플레이를 위한 규격

일반적으로 MIPI DCS(Display Command Set)을 사용 (D-PHY, C-PHY [DSI-2] 사용 가능)

동작

Command Mode, Video Mode 존재.

CM : DSI 규격에 정의된 MIPI DCS 사용

VM : 호스트 processor가 직접 화면 제어

CSI

CSI (Camera Serial Interface)

카메라 모듈을 위한 규격 (Protocol)

I2C Protocol을 사용하여 CCI(Camera Control Interface)에서 카메라는 Slave, Processor는 Master로 동작

동작

I2C CCI에서 Processor는 I2C BUS를 사용하여 카메라를 제어

카메라에서 촬영된 이미지 Data는 Data Lane을 통해 전송

728x90

'FPGA' 카테고리의 다른 글

| SPI Interface - FPGA to Chip (0) | 2024.06.12 |

|---|---|

| SPI Interface Basic Concept (0) | 2024.06.12 |

| UART Interface (1) | 2024.06.11 |