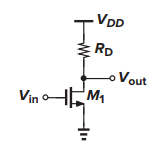

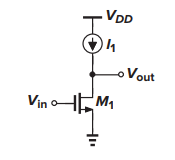

MOSFET은 기본적으로 Vgs에 걸리는 voltage값을 Id 라는 drain current로 convert 해주는 소자이다.

이때 CS stage의 구조는 이러한 MOSFET의 Gate에 입력을, Drain을 출력단자로 사용하는 형태이다.

이때 Drain단에 Rd 라는 저항을 달아 id의 Current값을 Vout에 Voltage의 형태로 변환해서 내보내는 구조이다.

즉, CS Stage는

1. input Voltage to Id Current

2. Id Current to output Voltage

의 과정을 거치는 변환 stage라고 생각할 수 있다.

(voltage 입력 voltage 출력)

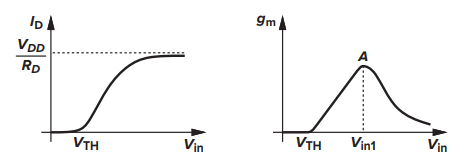

그렇다면 CS stage의 동작 특성을 알아보기 위해 Vin의 값을 변화시켜 보자.

1. M1 off, (Vin < Vth)

MOSFET에는 Id가 생성되지 않기 때문에 Rd에 발생되는 drop 또한 없다.

즉 Vout = Vdd

2. M1 on (Vin > Vth)

M1 트랜지스터는 Vth의 값을 넘어 소자가 on 된 시점부터 곧바로 saturation region에서 동작한다.

(why?) saturation 조건인 Vds > Vov 를 생각해 보았을 때.

M1 트랜지스터가 켜지는 순간 (Vgs - Vth의 값이 작은 순간)의 값은 Vds보다 필연적으로 작다.

(Vdd는 통상 높은 전압값으로 set)

따라서 M1이 켜져 Saturation region에 해당하는 Id만큼 전류가 Rd에 흐르므로

이와 같이 출력에 변화가 생긴다.

3. M1 동작점이 triode로 넘어갈 때 (Vds < Vov)

Vin의 크기를 더 늘려주게 되면 Vgs - Vth의 값이 점점 상승한다.

동시에 saturation region의 Id가 계속해서 크게 흐르면서

Rd에 걸리는 drop이 커지며 Vout이 작아지게 된다.

Vov값이 Vds의 값을 넘어가는 순간부터는 동작 조건에 의해 Triode region에 돌입하게 된다.

이때부터는 triode region의 Id 전류값이 흐르기 시작하므로

이와 같이 출력 전압이 생성된다.

즉, 정리하자면

1. cut off

2. saturation region

3. triode region

총 3가지 동작을 기준으로 CS stage의 동작 특성을 나누어 볼 수 있다.

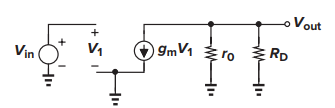

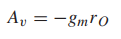

<Small Signal Gain>

CS stage의 MOSFET이 saturation region에서 동작할 때

small signal gain. 즉 Vout/Vin의 변화량을 구해보면

이때 small signal 이라는 개념 자체는

Circuit에 인가되는 신호가 Swing 하면서 회로의 동작 특성이 변한다 (region이 변화한다)

이러한 상황은 즉 nonlinearity를 발생시키는 요인이고 회로의 특성을 파악하기가 어려워진다.

따라서 회로 특성을 더 간단히 파악하기 위해

특정 bias level이 걸려있는 상태에서

이 bias level에서 회로가 보이는 특성을 보이는 특성을 유지한 채로

작은 진폭의 small signal을 통해서 회로를 동작시킨다.

즉, 회로를 예측 가능한 level 범위 내에서 동작시키는 것이다.

위의 CS stage를 예시로 들었을 때

small signal gain이 -gm*Rd 으로 구해진다.

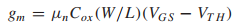

이때 gm은

위의 수식과 같이 Vgs

즉 Vin의 값에 따라서 변하는 요소이다.

만약 Vin 신호 자체가 매우 큰 범위의 swing으로 들어온다면

회로의 gain 자체가 gm의 변화에 따라 바뀌게 된다.

이는 곧 우리가 예측하기 힘든, nonlinearity 특성을 보이는 것이다.

<Transconductance - Vin relationship>

gm과 Vin의 관계식을 알아보자.

gm은 기본적으로 Vin에 대해서 drain current를 얼마나 흘려주는지에 대한 지표이다.

gm은 위의 수식과 같이 Vgs에 따라서 변하는 값이라는 것을 알았다.

Vin이 swing함에 따라 gm또한 변화하고, 결국 small signal gain이 변하면서 nonlinearity가 발생했다.

이에 따라 기본적으로 Voltage Gain을 명확히 짚어내려면 gm이 어떤 값을 가져야 하는지부터 정해야 한다.

즉, gm값을 가지기 위해 Vin이 어느 값을 가져야 하는지를 정해야 한다.

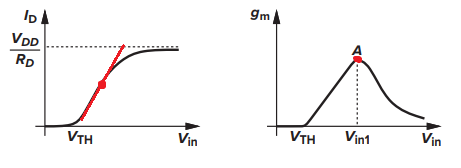

위의 그래프에 표시된 점은, gm의 관계 그래프에서

Vin 입력값에 따른 출력 전류 변화량의 최댓값을 의미한다.

즉 왼쪽 그래프의 변화량이 최대인 지점이 오른쪽의 Vin1의 gm 값인 고점 부분이다.

그렇다면 항상 gm을 위의 그래프에 표시된 최대 지점에서 동작시키는 것이 좋은가?

결론은

"상황에 따라 다르다" 이다.

결국 설계자가 어떤 특성을 가지는 회로를 설계한 것인가에 따라서 동작점이 달라진다는 것이다.

원하는 small-signal voltage gain이 무엇인지에 따라서 gm을 결정하고,

이를 위해 어떤 범위의 Vin 값을 설정해 주어야 하는지를 아는 순서를 거친다.

<trade-off relationship>

gm을 선정하기 위해서는 설계 목적이 있어야 한다.

이때 만약 Gain을 최대화 하는 관점에서(목적에서) 바라본다면 어떨까?

위에서 알아보았듯이 small signal gain은 -gm*Rd로 표현된다.

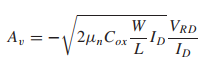

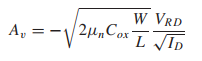

이때 gm과 Rd를 우리가 조작할 수 있는 변수가 들어있는 수식으로 변환해보자.

이 수식에서 조작할 수 있는 변수들을 찾아보면

Voltage Gain을 높이기 위해서

1. Aspect Ratio를 늘려주는 경우

2. VRD 값인 voltage drop 양을 늘려주는 경우

3. Id Current 양을 줄이는 경우

로 나눠볼 수 있다.

그런데, 이렇게 단순하게 생각했던 것과 달리

이러한 변수들을 변화시키면서 나타나는 Trade Off 가 발생한다.

1. Dimention을 늘리는 경우

Aspect Ratio를 늘이기 위해 width를 늘이거나 하면서 dimention을 늘이게 되면

device 자체의 크기가 커지면서

소자의 parasitic capacitance 값 또한 늘어나게 된다.

2. Rd drop을 늘이는 경우

Rd에 발생하는 Voltage drop이 커진다는 것은

Vout 단에서의 출력 전압 또한 낮아진다는 것이고

이는 곧 Voltage swing 범위를 제한하게 된다.

3. Id를 낮추는 경우

Vrd의 값을 유지하면서

무작정 Id를 줄이게 된다면

Vout단에서 원하는 출력값을 내기 위해 Rd의 값이 큰 소자를 사용해야 한다.

이는 출력단에서의 Time constant

즉 Delay 측면에서 큰 손해를 가져온다.

추가적으로 Rd 값이 커지게 되면

CLM의 효과 또한 상대적으로 커지게 된다.

(why?) Rd와 ro가 병렬로 연결되어 있을 때.

일반적으로는 ro가 매우 큰 값을 가지면서

Rd의 값을 따라가지만

Rd 또한 무시하지 못할 정도로 커지게 되면

ro가 무한대의 저항이 아니고, finite한 값을 가지기 때문에

Outut 저항이 상대적으로 오히려 더 작아지게 된다.

...

이러한 결과들은 결국

Voltage Gain을 높이기 위해 희생되어야 하는 요소이며

이것을 Trade off 관계에 있다고 한다.

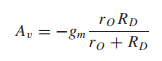

<CS stage biased with constant current source & intrinsic gain>

resistive load Rd 를

current source 로 대체해볼 수 있다.

ideal한 current source는

거의 무한대에 가까운 output impedance를 가진다.

즉, 무한대 저항과 ro의 병렬 저항이 load에 있다고 볼 수 있고

위와 같이 small signal gain을 얻을 수 있다.

이 gain값을 MOSFET 트랜지스터가 가지는 고유의 gain이라고 하여

intrinsic gain 이라고 부른다.

즉, 다시말해 MOSFET을 이용해 가질 수 있는 최대의 Gain 값이다.

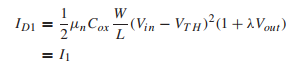

이렇게 Current source를 load로 가지는 stage의 vin/vout 관계식을 살펴보기 위해서는

Id의 수식에서부터 시작할 필요가 있다.

Vin은 2차 ,Vout은 1차의 형태로 Id를 이루고 있다.

constant current source로 Id1값이 고정되어 있다

Vin을 늘려주게 되면 Id1의 값을 유지하기 위해

Vout은 상대적으로 낮아져야 함을 알 수 있다.

이때 Vin이 2차식의 형태로

Vout보다 더 큰 영향력을 가지고 있기 때문에

Id1의 크기가 늘어날수록

Vin의 크기가 Vout에 비해 더욱 늘어난다.

'Circuit > Analog' 카테고리의 다른 글

| 3-2) Common Source Stage with Diode-connected Load (4) | 2024.09.04 |

|---|---|

| 3-0) Single Stage AMP (0) | 2024.09.04 |

| 2-2) MOSFET Structure and Symbols (0) | 2024.09.04 |

| 2-1) MOSFET as a Switch (0) | 2024.09.04 |