Chap. Physics of MOS Transistors.

MOSFET (Metal-Oxide-Semiconduvtor-Field-Effect-Transistor)

- Metal-Oxide-Semiconductor (MOS) Capacitor

MOS는 한국어로 금속-산화물-반도체 라는 뜻으로. 그 구성요소에 대한 이름이다.

MOSFET의 구조를 이해하고 동작을 따라가기 위해선 MOS를 흔히 알고 있는 Cap과 비교하여 이해할 수 있다.

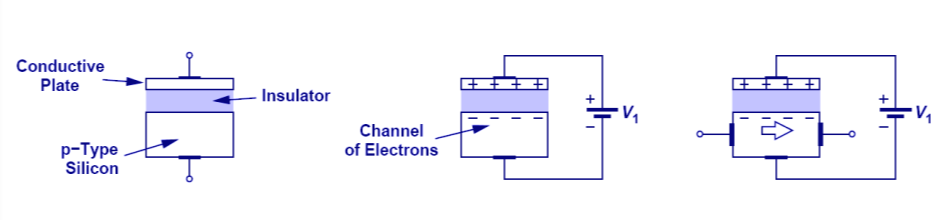

MOS는 위의 맨 왼쪽 그림과 같이. Conductive Plate, Insulator, P-Type Si (혹은 N type) 으로 구성되어 있다.

이는 마치 양쪽에 도체가 간격을 두고 떨어져 있고, 그 가운데에 부도체(절연체)가 들어가 Charge가 양쪽 도체(극판)에 쌓이게 되는 Capacitor와 같이 동작할 수 있다.

위의 MOS의 구조에서 Conductive Plate가 전극판으로, 가운데의 Insulator(Oxide 절연체)으로, P-Type Si가 도체의 역할로 대체되어 한쪽 전극판과 p-Si에 전압이 걸리게 됐을 때 Cap과 같은 상황과 동작을 하게 된다. (그림 중간)

이렇게 전압에 의해 Cap처럼 Charge를 가둬둘 때. p-Si 부분에 다시한번 전압을 걸어 전계를 생성시키면.

전압이 걸려있을 땐 충전된 Charge를 이동시킬 수 있게 된다. (선택적으로 Charge 이용 가능)

- Sturcture and Symbol of MOSFET

그렇다면 MOSFET (Metal-Oxide-Semiconduvtor-Field-Effect-Transistor) , MOS로 이루어진 전계 효과 트랜지스터는 어떠한 구조를 가지고 동작을 해 Tr.의 역할을 할 수 있을까.

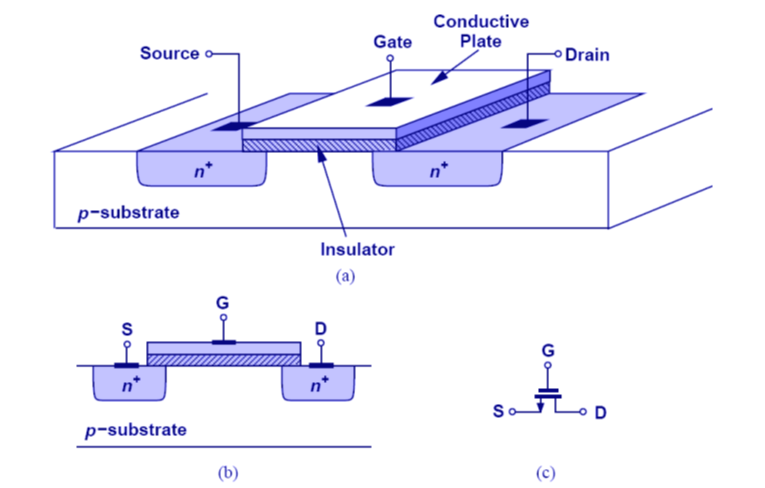

위의 단순한 MOS의 구조와는 달리. 우리가 궁극적으로 알고자 하는 MOSFET의 구조는 위의 그림과 같다.

구성요소로는 1. Source 2. Drain 3. Gate 4. Insulator 5. Substrate (P or N) 6. Conductive Plate (전극판) 이 있다.

여기서 먼저 가장 중요한 세가지 요소는 Source, Drain Gate 이며. MOSFET의 동작에 가장 중요한 역할을 한다.

먼저 Source 는 Charge가 공급되는 부분, Drain은 Charge가 빠져나가는 부분, Gate는 Tr.의 동작을 만들어준다.

이 때. Source와 Drain 단자는 다른 물질로 이루어진것이 아닌 Substrate위에 도핑된 (대부분 Wafer- P substrate)

즉 위의 그림의 상황에서 볼 때. P type의 기판에서 N type 도핑된 부분을 단자로 사용한다.

이러한 구조의 단면도가 (b), 회로에서 사용하는 Symbol이 (c)에 표시되어 있다.

이 때 Source 와 Drain 단자를 N+도핑된 영역으로 사용했다면 n-type MOS. 즉 NMOS라고 부른다.

(Symbol 화살표는 나가는 방향 -> Source에서 공급되는 Charge의 방향과 반대인 전류의 방향을 타나낸 것.)

Vs < Vd 이여야 Charge가 Source에서 공급된다. (전류는 반대)

MOSFET의 구조상에서, p-Substrate와 맞닿는 Source와 Drain은 일종의 PN Junction을 이루고 있다.

PN Junction은 다이오드로써 동작을 하고. 이 말은 S/D가 Sub. 보다 전압이 높을 때는 Revers Bias, 반대인 경우에는 Forward Bias 상태인 것으로 이해할 수 있다. (Sub.이 S/D보다 전압이 높으면 전류가 흐른다)

이렇게 다른 type의 반도체 물질을 결합시켜 Sub. 자체에 강한 전압이 걸리지 않는 한 전류가 통하지 않도록 하는 것을 Isolation이라고 하고, PN junction을 이용한 방식을 Juction Isolation 이라고 한다.

(MOSFET이 동작하기 위해서는 S/D와 Sub.사이에는 전류가 통하면 안되고, Sub.이 항상 낮은 전압을 가져야 한다.)

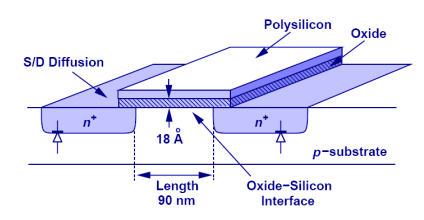

또한 다른 Isolation이 등장한 곳이 바로 Oxide를 사용한 Gate 부분인데. 이 부분의 산화물 두께를 Tox라고 한다.

Gate 전극과 S/D 사이의 전계효과를 만들어내기 위한 절연층이다. 이 절연층 두께가 두꺼워지거나 낮아짐에 따라 MOSFET의 동작 상태에 영향을 주게 된다.

또한 전계효과를 가지는 Channel의 길이와 폭 (Channel Length/Width) 또한 영향을 크게 미친다.

(이러한 구조의 두께, 길이가 변하면서 발생하는 효과는 뒤에서)

- Formation of Channel

MOSFET이 Tr.로써 동작하기 위해선 Charge가 Source와 Drain 사이에 통해야 하고. 위에서 살펴본 MOSFET의 구조에서는 Junction isolation에 의해 Charge가 이동할 공간이 없다.

이 때 Charge가 S/D 사이에 통하는 구간을 Channel이라고 하고, 이러한 Channel이 어떻게 생성되는지 볼 것이다.

1. Gate단에는 전압원이, Source, Drain 단자에는 GND를 형성해 준다.

2. Gate 전압인 Vg가 일정수준 미만의 약한 전압을 형성하면. Gate와 p-Substrate 간에 수직 방향 전기장이 생성되고, Sub.의 Carrier에 의한 공핍층 (Depletion Region) 이 형성된다. (전류가 흐르지 않음/Channel 이 형성되지 않음)

3. 계속해서 Vg를 높이면 Depletion Region 또한 늘어나게 되고, 일정 수준 이상의 전압 (분턱전압 Vth)이 Gate에 인가되면. 더이상 Depletion Region이 커지지 않고 반전층인 Inversion Layer가 생성된다.

(p-Type의 Substrate의 Majority Carrier인 정공이 Depletion Layer을 형성하고, 그 이상의 전압에 의해 Minority Carrier인 전자까지 끌려와 Insulator 밑에 전자들이 모여 n-Type의 층이 형성된다.)

4. 형성된 Inversion layer은 위와 같은 nMOS에서 Channel로 동작하고. S/D 단자에 전압을 인가하면 전류가 흐른다.

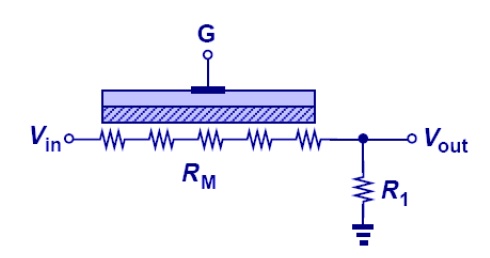

- Voltage-Dependant Resistor

위의 Channel 형성 과정에서, 전류가 통하고 통하지 않는 것을 다르게 생각해보면 Source와 Drain 단자 사이에 저항이 있는 것으로 이해해볼 수 있다.

공핍층만 형성되어 전류가 흐르지 못할때는 저항이 강한 것으로. Vth 이상의 전압이 걸려 S/D간의 전류가 흐르는 순간은 저항이 낮은 것으로 생각한다면. Gate 전압을 조절함으로써 S/D간의 저항을 조절할 수 있다는 뜻이다.

이러한 특성을 이용해서 파형의 위상은 바꾸지 않고 폭만 바꿔주는 Attenuator (감쇠기) 또한 생각해볼 수 있다.

전압 분배 법칙에 의해서 Rm과 R1의 관계를 Vout의 입장에서 살펴보면

이고. 이를 이용해 Gate 전압을 조절하여 Rm의 값을 조절할 수 있고. 결국 Vout에 대한 출력 또한 조절할 수 있다.

이렇게 Vin에 대한 Vout의 값을 Vg의 변화로 조절하면서 Vin의 진폭을 조절하는 감쇠기를 설계할 수 있다.

- MOSFET 특성

위에서 한번 언급했듯이. 단순히 반전층이 Vg에 의해 형성됐다고 해서 전류가 S/D사이에 흐르는 것이 아닌. 한쪽에 전압을 걸어 전기장을 형성해 주어야 전류가 흐른다. (Charge가 이동한다)

우리가 설정한 Source와 Drain을 정했다면. Drain 부에 전압을 걸어주고 Source 단자에 GND를 연결해 주면 전류가 통한다. (Drain 단자가 항상 Source 단자의 전압보다 높아야 Charge가 Source에서 Drain으로 이동함으로.)

오른쪽의 그림은 설계 회로도에서 표시하는 방법을 나타낸 것.

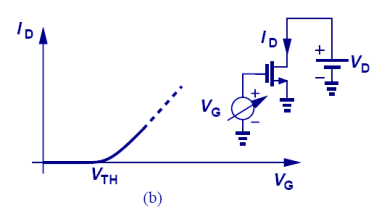

(b)의 그림은 Drain 전압을 고정하고 Vg의 전압을 서서히 올려서 전류가 어떠한 특성을 가지고 흐르는지 관찰한 것이다.

Vg가 Vth 문턱전압을 넘는 순간부터 전류가 S/D사이에 흐르기 시작하고, 그림상에서는 Linear 하게 증가하는 것 처럼 보이지만. 실제론 Exponential 형태로 증가한다.

(c)의 그림에서는 (b)의 상황과 반대로. Vg를 Vth 이상의 값으로 고정시켜 항상 On 해놓는다.

이후 Drain 전압에 변화를 주면서 전류를 관찰한다. 위에서 알아봤듯이 저항의 관계로 이해할 수 있으므로.

V=IR과 같은 옴의 법칙 형태로 Linear하게 그려진다.

(d)의 그림에서는 (c)의 상황에서 Vg의 값이 Vth 이상의 값에서 증가될 때. Vg의 값이 크면 클수록 전류의 변화량 (기울기)가 증가하는 것을 볼 수 있다.

이 또한 저항의 관계로써 생각해 보았을 때. Vg의 증가로 인한 저항 R의 감소로 전류 I의 값이 더 커진 것으로 이해할 수 있다.

이러한 결과로 Vg의 전압값이 크면 클수록 전압의 변화가 크므로, MOSFET의 반응속도가 증가한다는 것을 알 수 있다.

- Channel Length와 Tox(산화막 두께)에 의한 영향

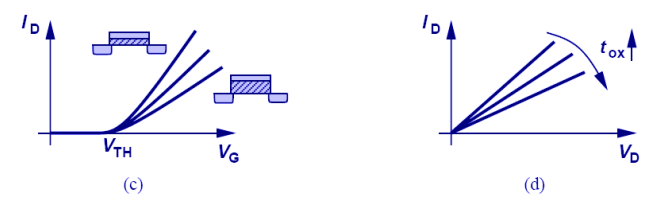

Channel Length에 의한 영향은 단순하게 전류가 흐를 수 있는 도선을 생각해 보면 쉽다.

같은 저항값, 두께를 가진 도선은 길이가 길어지면 길어질수록 저항 R의 값이 커진다.

Channel 또한 마찬가지로 Charge가 이동하는 것이므로. Channel이 길어지면 길어질수록 Charge의 이동이 어려워진다.

따라서 (b)의 그래프와 같이 Length가 길어지면 기울기값이 낮아지는 것을 볼 수 있다.

이것으로 MOSFET의 Channl Length는 짧을수록 반응속도가 더 빠르다는 것을 알 수 있다.

다음은 Insulator인 Oxide의 두께 Tox에 의한 영향이다.

위의 산화막 Capacitance 수식에서 산화막 두께에 해당되는 Tox의 값이 크면 커질수록 (두께가 두꺼워질수록) Cox값, 즉 산화막 Capacitance가 감소하고. 산화막의 Cap이 감소한다는 것은 Gate단과 밑의 Sub사이에 걸리는 전기장의 세기가 줄어든다는 것이다.

결국 전기장의 세기가 줄어들면 Vg에 의한 Id의 영향을 보았듯이. 전류량이 줄어든다.

따라서 산화막의 두께 증가는 전류 값의 변화 (기울기)를 작게 만든다.

- MOSFET의 Gate Width값 영향.

Gate의 Length와 Width는 결국 Channel의 Length와 Width에 직접적인 영향을 주는 요인이다.

결국 Gate Width의 증가는 Channel Width의 증가와 동일하고. 이는 Channel의 저항의 관점에서 저항이 낮아지는 결과가 나타난다.

따라서 (b)와 (c)의 그래프에서 볼 수 있듯이. Gate Width값이 커질수록 전류의 증가량이 증가하는것을 볼 수 있다.

※

MOSFET에서 Gate Voltage에 의한 Channel의 R 관점에서. 실제 MOSFET이 설계된 회로 내에서의 동작속도는 RC Delay에 의해서 결정되고, 이것의 값은 R x C의 값으로 이루어진다.

따라서 MOSFET의 속도는 R의 값을 줄여야 한다.

이는 위에서 알아보았듯이. R이 감소하면서 흐르는 Id의 변화량(기울기)를 가파르게 만들 수 있는 요인들은 모두 MOSFET의 속도에 영향을 미친다는 것을 알 수 있다.

- Formation of Channel (Potential Difference)

지금까지 생각했던 MOSFET의 Channel의 형성은 일정한 두께를 가지고(일정한 Potential을 가지고) 형성되는 것으로 생각했었다. 하지만 실제 MOSFET에서 Channel 형성에 기여하는 요인들은 Vg와 Sub.의 전위차이인 Vg-Vb의 크기와 Drain 전극에 걸리는 전압의 크기인 Vd에 대해서 Vg와의 전위차인 Vg-Vd의 값이다.

즉, Channel 형성에 가장 큰 영향을 미치는 두 값은 1.Gate와 Sub.에 걸리는 전기장의 세기 2. Gate와 Drain의 전위차.

만약 우리가 생각했듯이 Channel의 두께가 일정하게 퍼져서 형성되어 있어야 한다면. 두가지 값이 MOSFET Channel 내에서 일정하다는 것이다.

하지만 실제 MOSFET에서는 Drain 부분에만 전압이 걸리므로. Vg가 일정한 상황에서 Vg-Vb의 값은 일정하지만, Vg-Vd의 값은 위치에 따라 변화한다는 것이다. (그림 a에서 볼 수 있다)

그렇다면 형성되는 반전층인 Inversion Layer이 일정하게 형성되지 않는다는 것이고. 이는 곧 Channel의 두께가 Source 부분과 Drain 부분에서 차이가 난다는 것을 알 수 있다.

위의 (b) 그림에서 볼 수 있듯이. Gate와 Drain간의 전위차 Vg-Vd값은 같은 +값의 전압이 걸리는 Drain 전극쪽에서 가장 작게 나타나고. GND 취급 (낮은 전압을 인가한) Source전극 부분에서의 Gate 전극과의 전위차 Vg-Vs가 가장 큰 것을 알 수 있다.

정리하자면. Gate와 Source, Drain 간의 전위차는 서로 같지 않고 한 쪽으로 쏠려 있으며, 이는 곧 Channel 형성, 혹은 Inversion layer 형성에 영향을 미치고, 전위차의 크기가 큰 쪽에서 더 강한 전기장이 형성되므로 Inversion layer 혹은 Channel의 두께는 양전압이 걸리는 Drain 전극 부분보다 더 두꺼운 층을 형성하게 된다.

- Channel Pinch-Off

그렇다면 Drain의 전압을 Gate와 거의 동일할 정도로 증가시킨 상태에서의 Channel은 어떻게 생성될까?

위에서 알아보았듯이 Vg-Vd 의 값. 즉 Gate극과 Drain전극의 전위차이가 S/D간에 서로 달랐다.

그러나 Drain 전압 Vd를 Vg 수준으로 증가시키면 두 전위차의 크기가 0이 되고. Channel이 형성되지 않는다.

그렇다면 S/D간의 전류 또한 끊어질 것이라고 생각할 수 있다. 하지만 실제로는 전류가 흐를 수 있다.

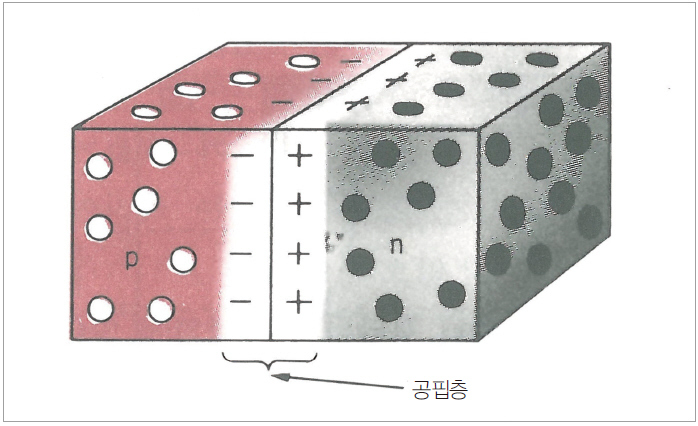

먼저 공핍층에 대해서 약간의 배경지식을 깔고 가자면.

PN Junction 사이에는 서로간의 도핑된 물질로 인해 Majority Carrier가 존재하고. 각 반대되는 극성을 가진다.

이렇게 다른 극성을 가진 물질을 붙여놓으면, 서로간의 쉽게 움직일 수 있는 Carrier들이 밀려나고 그 자리에는 본래의 이온들만이 남게 된다. 이렇게 되면 움직이지 못하는 이온들은 도핑에 의해 (-), (+)로 극성을 띄고 있으므로. 접합부 사이에서 전기장을 이루고 있다.

이때 가운데에 형성된 전기장의 층을 공핍영역, Depletion Area라고 한다.

이렇게 형성된 공핍영역에서는 외부에서 P type 도핑된 곳에 N-type보다 높은 전압을 걸어주지 않는 한 전류가 흐르지 않는다. (다이오드의 특성)

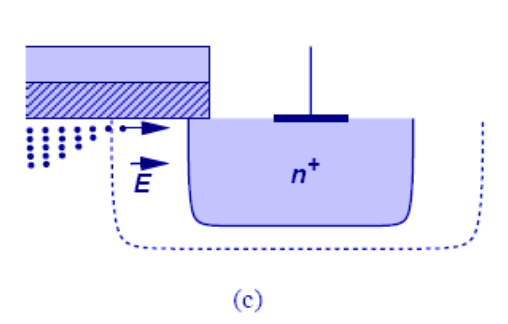

위의 (c)의 그림을 자세히 보면. Drain 전극으로 사용되는 n+ 도핑층은 현재 Substrate와 PN Junction 관계이다.

이 때 PN Junction으로 인해 생성된 공핍층이 (c)의 그림에서 점선으로 표시된 부위만큼 형성되어 있는 것이다.

그러나 우리가 전압을 걸어주는 Drain 단자는 n+도핑된 곳이므로. 양방향의 전압을 강하게 걸어주면 걸어줄수록 공핍층이 점점 두꺼워진다. (역방향 Bias를 걸어주고 있으므로)

이 공핍층 내에서는 전계가 E방향으로 형성되어 있는데, 이 때 Pinch-Off 된 Channel에서 이 공핍층 영역의 Edge부분에 닿는 순간부터 Channel을 통해 들어온 Charge는 곧바로 E의 반대방향으로 가속해 Drain 단자에 닿게 된다.

이러한 원리로 실제 형성된 Channel은 Drain 단자에 닿지 못했지만. Drain단자의 공핍층 영역 Edge부분에 닿을 만큼만 된다면 전류가 흐를 수 있는 것이다.

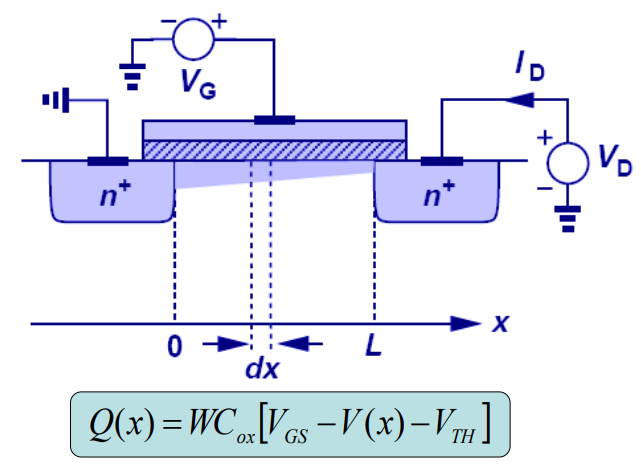

- Channel Charge Density

그렇다면 이렇게 형성된 Channel 내에서의 Charge Density를 알 수 있는 방법을 알아보자.

기본적으로 Channel Charge Density는 Channel의 단위 길이(Length)에 있는 Charge density 이므로.

Length는 단위 1의 값으로 고정시키고. 면적에 대한 정보는 Cox로 표시된 절연막의 Capacitance가 산화막의 두께와 유전율로 이루어진 단위로서 면적의 의미를 내포할 수 있게 되고, 또한 Gate와 Source간의 전위차에 문턱전압 Vth를 뺀 만큼 비례하게 된다.

'반도체 소자, 회로설계 > MOSFET' 카테고리의 다른 글

| MOS 와 MOSFET (4) - Large / Small-Signal Models, PMOS tr. (1) | 2022.03.30 |

|---|---|

| MOS 와 MOSFET (3) - gm의 조작 / Velocity Saturation / Body Effect (0) | 2022.03.29 |

| MOS 와 MOSFET (2) - 정량적 이해 (5) | 2022.03.23 |