- Large-Signal Models / Small-Signal Models

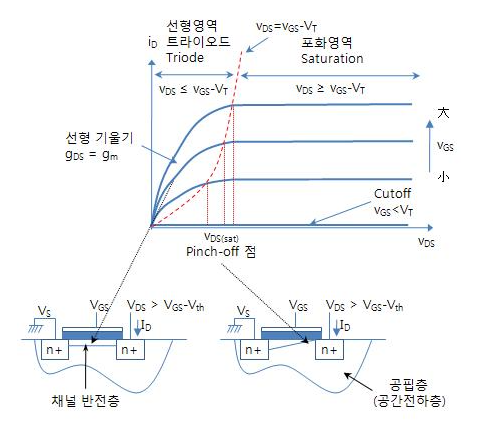

우리가 앞서 파악한 Drain에 흐르는 최대전류(혹은 Channel의 최대전류/Saturation Current)는 다음과 같다.

이 모델의 식에서. 위의 그래프와 같은 2차 곡선의 형태로 나타낼 수 있고, 이 식을 통해서 값을 Traking 할 수 있다.

즉 이말은 모든 변수 영역에서 Id의 정확한 값을 찾아낼 수 있다는 것이다. 이를 Large-Signal Modles 라고 한다.

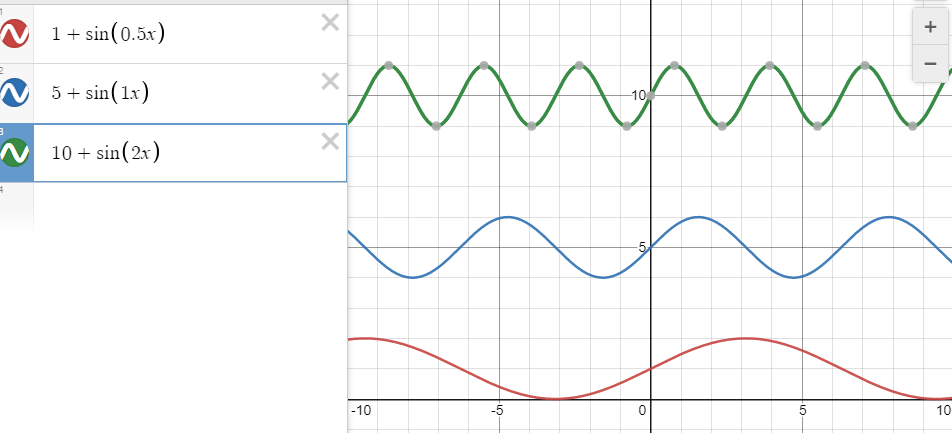

입력되는 신호는 AC의 값이라고 가정할 경우. 특정 Static의 값을 가지고 특정 형태의 Wave를 가진다.

위의 그래프에서 Static의 값은 Y축을 지나는 값. 즉 x=0인 부분, 어느 위치에서 DC신호가 들어오는지 이고, 뒤의 위상변화와 Wave를 뜻하는 Sin / cos 등과 wt라는 변수로 입력된다.

이때 기본 Id 식의 형태를 보면 알 수 있듯이. 기본적으로 식의 형태가 Exponential 형태이고. 계산이 복잡하다.

이러한 특성 때문에 Static, DC voltage 즉 Static의 간단한 값을 정확히 계산할 때 사용하게 된다.

여기서 우리는 뒤의 특정 자그마한 영역에서의 Signal에 대해 볼 수도 있을 것이다.

뒤의 Wave로 들어오는 형태의 Signal을 알아내기 위해서는 Small-Signal Model을 사용한다.

위의 2차식에서 특정 변수 부근의 값이 들어오게 될 때. 그 지점의 Id값의 변화량은 곧 앞서 배운 gm(Transcond.) 이다.

이는 Id의 값을 미분하여 얻어지기 때문에. 2차식의 형태인 Id를 미분하여 얻은 gm은 1차식의 형태로 나타난다.

Linear 함수로 더 간단하게 그 특정 부근에서의 Signal을 알아낼 수 있고. 따라서 복잡한 형태로 들어오는 Dynamic, AC의 형태인 뒷부분 Signal을 계산할 때 사용된다.

이때 AC 값의 계산은 그 구간에서 구해진 gm의 값과 그 값으로 계산된 Magnitute값을 곱해서 구해진다.

-> gm * Mag

최종 입력 Signal을 알아낼 때에는, Large-model을 이용하여 Static 값 위치를 알아내고, Small-model을 이용하여 정확한 파형을 계산하여 둘을 더한 값으로 알아낼 수 있다.

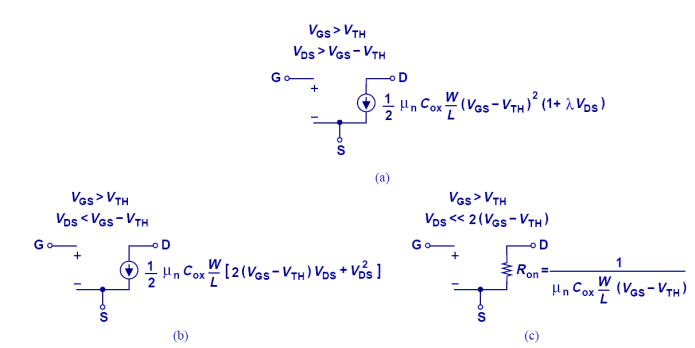

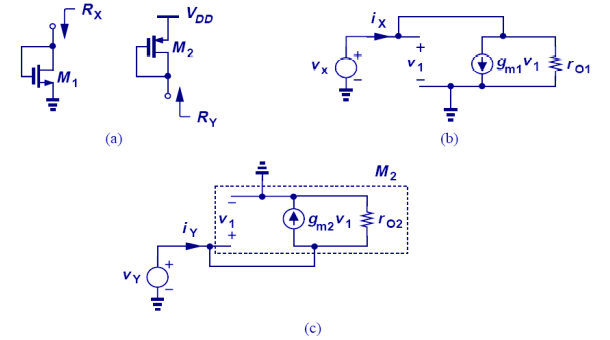

Small-Sginal Model에서는 앞서 설명했던것이 Drain의 전류원을 gm과 Vgs의 곱으로 나타내었다.

이때 (a)는 Channel Length Modultation 효과를 적용하지 않은 것이고, (b)는 효과를 적용한 것이다.

Channel length Modulation에 의한 λ term의 효과를 나타낸 전류식은 다음과 같다.

또한 gm을 나타내는 수식은 다음과 같고 이는 옴의 법칙에 근거해 보자면 저항의 역수값이다.

따라서 위의 Id 수식을 Vds에 대해서 미분을 하면 Modulation 효과가 없을때의 전류식 Id에 λ을 곱한값으로 나오므로.

이는 사실상 Modulation 효과를 고려했을 때 완벽한 =의 기호가 아닌 거의 유사한 수준이다.

이를 최종적으로 저항의 관점으로 바꾸어 역수를 취해준 것이 바로 위의 수식이다.

이러한 저항의 값이 커질수록 Id의 변화가 작아진다는 것을 알 수 있으므로.

Id의 값이 ideal하기 위해선 Channel length가 커야하고, Length가 크면 R이 커진다는 뜻으로 이해할 수 있다.

-> λ의 영향이 커질수록 Modulation 효과가 커진다. -> Id의 변화가 심해진다.

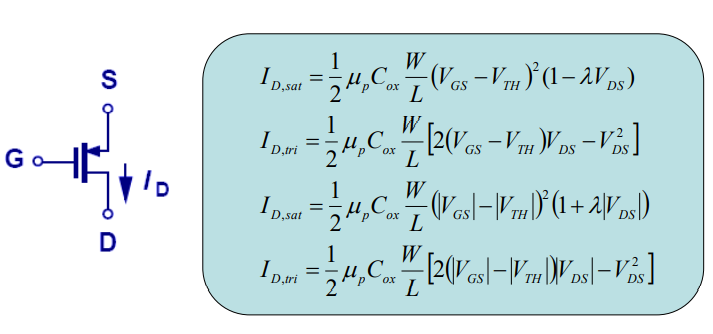

- PMOS Tr.의 경우

NMOS와 PMOS는 정반대로 동작한다. NMOS는 게이트 전압이 Vdd일 때 채널이 형성되어 ON되고, 게이트 전압이 0V일 때 OFF된다. PMOS는 반대로 게이트 전압이 Vdd일 때 OFF, 0V일 때 ON으로 이해할 수 있다. (공핍형)

PMOS는 NMOS와 반대의 동작을 하기 때문에, 부호의 복잡성을 제거하고 절대값의 term으로 수식을 계산한다.

또한 mobility 자체도 Carrier가 Hole과 Electron으로 서로 상이하기 때문에 Hole에 대한 mobility로 쓴다.

(hole의 mobility는 Electron에 비해 두~세배 작다)

*타 성능이 다 똑같다고 했을 때. mobility 차이와 well공정 차이 때문에 NMOS로 대체할 수 있다면 대체하는 것이 설계의 입장에서 합리적이다.

CMOS Logic을 이용, DC current를 줄이기 위해 PMOS 같이 이용(NMOS는 Current소모 큼), 집적도는 PMOS가 NMOS의 크기보다 두배정도 더 차지함.

'반도체 소자, 회로설계 > MOSFET' 카테고리의 다른 글

| MOS 와 MOSFET (3) - gm의 조작 / Velocity Saturation / Body Effect (0) | 2022.03.29 |

|---|---|

| MOS 와 MOSFET (2) - 정량적 이해 (5) | 2022.03.23 |

| MOS 와 MOSFET (1) - 정성적 이해 (0) | 2022.03.16 |