- Amp란? - 입력 signal을 일정한 비율로 (Gain의 선형성) 증폭시켜주는 Device (형태는 같고 크기는 다른)

- Gain = Vout / Vin

- 이때 주의해야 할 것은, 단순히 AMP가 1V의 입력을 넣으면 2V, 2V 입력을 넣으면 4V 로 바뀌는 동작을 하는 것이 아니라, "기준 전압값 대비 변화량" 을 증폭시킨다는 점이다.

- 또한 Amp의 입출력으로는 전압, 전류가 될 수 있지만 대표적으로 Voltage input Voltage output AMP를 볼 것이다.

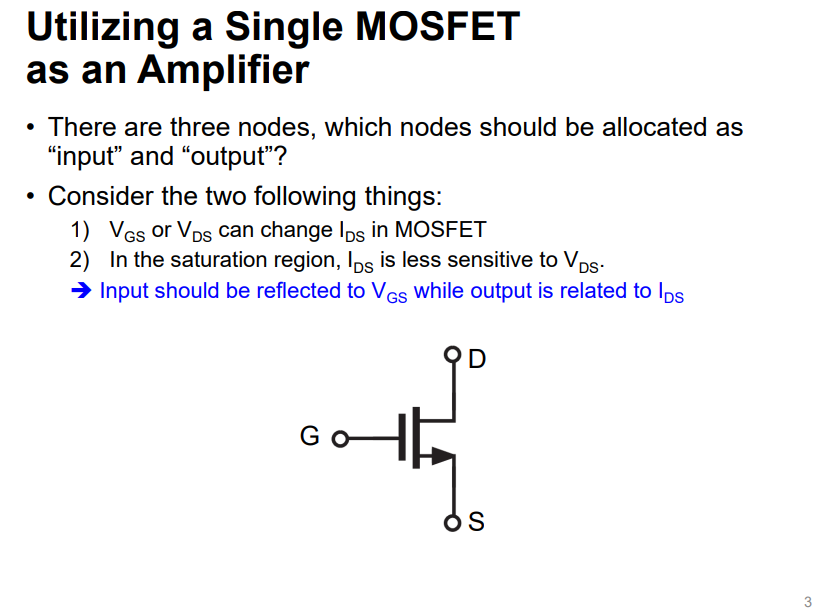

- MOSFET에는 3가지 node가 존재한다 (Body는 일단 제외)

- MOSFET의 어떤 Node를 Input으로 사용할지, Output으로 사용할지 정할 수 있어야 한다.

- 위와 같은 전류식의 형태를 볼 때 Id를 제일 잘 변화시킬 수 있는 전압값은 Vgs, Vds 값이다.

- 이때 Vds값은 Saturation 영역 관점에서 Id 전체 값에 미칠 수 있는 변화의 양이 작기 때문에 입력으로 쓰는건 부적절하다.

- 즉, Id를 바꾸기 위한 Node로 Gate단을 택해 Vgs를 입력으로 받아 Vgs값의 변화가 Id에 나타날 수 있도록 (출력 노드로 사용할 수 있도록) 하는것이 바람직한 선택일 것이다.

Input Voltage를 Vg node에, Output Voltage를 Vd node에서 인가하고 측정해볼 수 있다.

- 우리는 위의 논리와 같이, Vgs에 영향을 줄 수 있는 Input node와 Id의 변화를 받아올 수 있는 출력 node를 동일하게 적용해볼 경우 가능한 3가지 경우의 수를 꼽을 수 있다.

- 위의 그림과 같이 Common Source, Common Drain, Common Gate의 3가지 형태로 부른다.

- 이름이 붙여진 원리는 In/Out으로 사용되는 node를 제외하고 나머지 한 node를 공통(Common)하게 쓴다는 것에서 특징을 살려 붙인 것이다.

이 중에서도 오늘 게시물에서는 가장 대표적인 topology 형태인 Common Source 형태를 먼저 살펴볼 것이다.

- CS stage의 전체적인 구조를 보았을 때, Vgs의 값을 변화하여 Ids 값을 변화시켜 Drain node에서 전류 변화에 따른 전압 변화를 측정한다는 원리를 유추할 수 있다.

- CS stage에서 세가지 의문점이 생길 수 있다면.

- Vgs의 변화량을 정확히 인가하기 위한 Source node는 어떤 값으로 Fix 할 것인가? (GND fix)

- 어떻게 Vout 변화량을 측정해낼 것인가? (저항의 사용)

- MOSFET이 Triode/Saturation 영역중 어느 영역에서 동작하도록 환경을 setup해 주어야 하는지. (saturation)

- 첫번째 의문에 대한 해답은 간단히 해결해 볼 수 있다.

- Vg의 변화량을 가장 정확하고 직관적으로 판단할 수 있는 방법은 하나의 기준점을 GND로 두어 0을 만드는 것이다.

- MOSFET은 Vg 전압값을 이용한 가변저항 이라고 생각할 수 있다고 했다.

- 이때 MOSFET을 하나의 가변저항이라고 생각한다면, Drain node에서 저항변화에 따른 전압 변화량을 관찰하기 위한 방법은 무엇이 있을까?

→ Vdd 고정 전압, Rd 고정 저항을 추가해준다.

- 이렇게 되면 저항 분배에 의해 Rs가 Vg에 의해 변화하는 값을 Voltage 측면에서 얻어낼 수 있다.

즉, Vg 입력 변화 → Vg - GND(0) 으로 변화량 감지 → Ids 변화 → Rd의 전압강하 변화 → Vout 변화

- 이때 CS stage의 Gain은 어떻게 계산해볼 수 있을까?

- 변환 과정에서 Vgs의 변화량 대비 Ids 변화량을 Transconductance라고 칭하고 gm의 기호로 사용한다.

→ CS stage Gain : Vout/Vin = -gm * Rd

gm값인 Transconductance의 계산은 곧 Id의 수식에서 Vgs로 나누어 준 값이라는 것 또한 알 수 있다.

그렇다면 Saturation, Triode 영역의 Id 값 중 어느 것을 택해서 사용해야 할까? (MOSFET 동작 영역을 어디로?)

- 각 동작 영역에 따른 전류 수식을 보았을 때. Vd인 출력 node의 영향을 가장 적게 받아야 한다는 점을 알아야 한다.

- 즉, Triode 영역의 수식을 보았을 때 Dominant한 변수값은 Vds이므로, AMP의 동작 영역으로 부적절하다.

- 반대로 Saturation 영역의 경우, Dominant한 변수값은 Vgs이므로 AMP의 동작 영역으로 적절하다.

→ 결론적으로 무조건 MOSFET이 Saturation 영역에서 동작하게 하여야 한다. (Vgs>Vth, Vds>Vgs-Vth(Vov))

- AMP로써 동작시키기 위해 saturation 영역에서 동작시키는 조건을 만들어 주는 작업을 Biasing 이라고 한다.

- Vgs > Vth 조건을 만족시키기 위해 Vg node에 R1, R2로 구성된 전압분배 회로로 Vth보다 높은 전압을 인가한다 (입력단 기준전압 or 동작영역 Bias)

- Vds > Vgs - Vth 조건을 만족시키기 위해서 saturation 영역에서의 Id 값을 고려해 Rd 값을 setting 해주어야 한다. (출력단 bias)

이를 통해 MOSFET의 입력값이 들어온 직후 바로 Saturation 영역에서 동작할 수 있도록 Bias 해주는 작업을 거쳐야 한다.

- Bias 작업이 입력단에 되어있을 경우, 실제 Signal input을 어떻게 인가할까?

- 이때는 coupling capacitor 라는 cap을 입력단에 추가하여 input signal을 인가한다.

이때 쓰이는 입력단의 capacitor는 DC noise 간섭을 줄이고, 각 stage마다의 load effect를 줄이는 효과가 있다.

또한 bias 회로 관점에서도 cap의 양단의 전압은 계속해서 서로 따라가기 때문에 bias에 영향을 미칠 일도 없다.

Practice

- Vgs 값을 결정하는 X node와, Vds를 결정하는 Y node가 따로결정될 경우 조건에 따라 동작조건이 달라진다.

- 하지만 만약 Vg 값을 Vd와 동일하게 연결할 경우, Saturation 조건인 Vds > Vgs - Vth 를 무조건 달성할 수 있게 된다.

→ Self-Biased MOS stage.

Practice

- CS stage의 concept로 다시 돌아와서 생각해 보자.

- Vin의 변화가 Vgs를 변화시키고 Ids를 변화시키고 최종적으로 Vout값을 변화시킨다.

- Vgs > Ids > Vout으로 변해가는 과정에서 AMP의 특성인 linearity를 만족해야 한다.

- CS stage의 구조를 보았을 때.

- Vin (bias) + ΔVin (Signal)

- Id (bias에 의한) + ΔId (Signal에 의한)

- Vout (bias에 의한) + ΔVout ( ΔId에 의한 전압강하로 (Rd))

- 위의 과정을 거치면서 Signal이 전달된다. 이러한 Signal이 linear한 Vout/Vin의 비율을 따르려면 결국 1차원적으로 생각해 보았을 때, ΔVin의 변화에 의한 ΔId 변화가 일정해야 한다. (Transconductance)

- 그러나 기본적으로 saturation 동작의 Id current 값은 Vgs변수에 대해서 2차식의 형태를 갖고 있다.

→ 이때, 매우 작은 range에서의 ΔVin은, 2차식 내에서 매우 가까운 거리의 변화를 쟀을 때 처럼 1차식의 형태로 취급하여 사용할 수 있다. (small signal)

→ 이때의 일정한 기울기로 assume 된 값이 gm, 즉 Transconductance 값이다.

다시한번 정리하자면,

- Bias condition을 제외하고, Small Signal에 의한 변화의 값만 집중해서 보자.

- Vgs (bias) + ΔVgs (Signal) → vgs

- Vin (bias) + ΔVin (Signal) → vin

- Id (bias에 의한) + ΔId (Signal에 의한) → id

- Vout (bias에 의한) + ΔVout ( ΔId에 의한 전압강하로 (Rd)) → vout

- Vds (bias) + ΔVds (Signal) → vds

→ Bias condition을 제외한 값으로 치환하여 간편하게 계산할 수 있다.

- 이때 Signal의 range를 Small signal, 즉 id의 vgs 값에 대한 미분 조건이라고 생각할 수 있다

- 이러한 조건을 생각해 보았을 때, CS stage 자체를 Small signal model로 modeling 해볼 수 있다.

- 이제부터는 변화량 자체를 하나의 변수값으로 놓고 사용할 수 있게 되었다. (dc값은 gnd 처리)

- 이때 Id = gm * V1 이라는 gm값에 대한 표현으로 사용할 수 있다. (gm이 bias에 의한 상수값이 되었기 때문)

- 이제 CS stage를 직관적으로 이해해보자

- Vin의 변화가 Id의 변화를 가져오는 것 자체가 gm의 값, 즉 transconductance이다.

- Vout의 변화를 불러오는건 Id의 변화 때문이고, 이는 Rd에 의해 전압으로 전환된다. 즉 Rd의 값이 주요하다.

→ Av (gain) = - gm * Rd

- (-)의 값은 small signal 관점에서 vin이 (+) 일 때 vout (-) 의 관계를 가져오는 상태를 의미한다.

- 이때 모든 MOSFET의 동작 영역은 Saturation 기준으로 사용됐다는 것을 기억해야 한다.

- 단순히 bias에 의한 id의 값이 큰 MOSFET (gm의 값이 큰)을 사용하여 id값을 끌어올려 높은 gain을 얻고자 할 때

Vdd - Rd * Id > Vgs - Vth

- 무작정 Id 값을 크게 하여 사용한다면, Saturation 동작 조건 자체가 깨질 수 있다.

Practice

'Micro 전자회로 (Docceptor 강의)' 카테고리의 다른 글

| 3-1) Input/Output Resistance (0) | 2024.07.10 |

|---|---|

| 2-3) Additional Current path + Channel Length Modulation Effect in CS Stage (0) | 2024.06.27 |

| 2-2) Common Source Amplifier (CS Stage) - CLM effect 반영 (0) | 2024.06.26 |

| 1-2) Operation of MOSFET, Qualitative Respect (1) | 2024.06.12 |

| 1-1) Micro Circuit 이란, Silicon 특성 기초 (2) | 2024.06.11 |