728x90

※ Degeneration 구조를 사용하는 이유?

- Gain 안정화 (기존 gmRd의 형태에서 저항이 가지는 불안정함을 해소)

- 선형성 향상 (Gain 값은 작아지지만, 안정화 되면서 선형성 향상)

- 입력 임피던스 증가 (Signal 입력으로부터 더 적은 전류를 생성 → gain 입장에서는 bad)

- 온도 안정성 향상 (온도 변화에 따른 gm값의 변동, 저항값의 변동을 최소화)

→ 신호 왜곡 감소 및 환경변수 최소화

이번에는 CS Stage의 구조에서 Rs를 추가하였을 때의 Gain을 구해보자.

- Degeneration 구조에서 Rs가 추가되면서 생기는 문제점은 Vgs 값에 영향을 미친다는 것이다.

- 그동안 MOSFET의 source는 gnd 처리되어 Vgs = Vg - Vs = Vg - 0 형태로 Vin = Vg = Vgs로 온전히 사용됐다.

- 하지만 Rs의 존재로 Vgs = Vg - Vs = Vg - idRs 라는 값으로 변한다.

→ 입력이 온전히 사용되던 것과 달리, Vgs, idRs 형태로 Vin의 영향력이 쪼개진다.

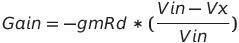

- 즉, 기존 Gain값인 -gmRd의 형태에서 Vin에 영향이 미치는 Ratio (손해요소) 만큼 곱해주어야 한다.

Source의 전압값을 Vx라고 할 때.

위와 같이 계산되어야 한다.

의 과정을 거치면

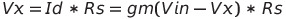

Small Signal 기준으로 구해볼 수도 있다.

∵ ΔId/ ΔVgs = gm

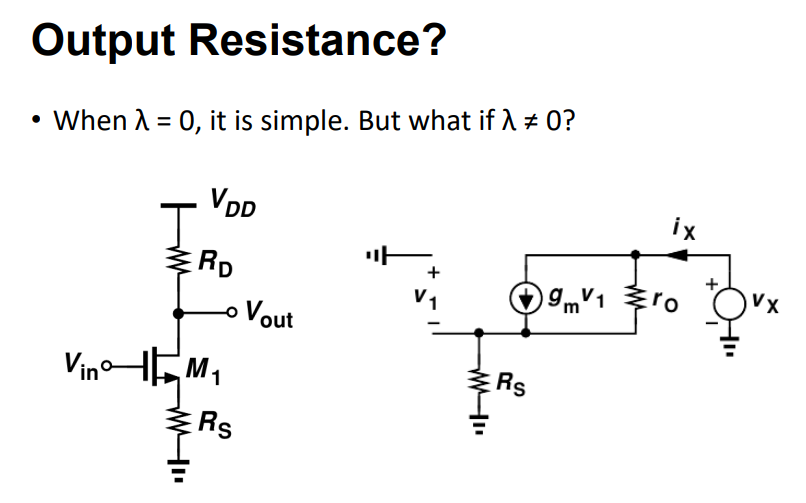

Degeneration CS Stage의 output Resistance 특성은 어떠한지 살펴보자.

- Output Resistance를 구하는 방법 또한, Vout node에서 Vx라는 임의의 전압원을 인가하여 구해낼 수 있다.

- Vout node 기준 Rd 방향으로 보이는 저항, M1 방향으로 보이는 저항 두가지가 있을 것이다.

- M1 방향으로 보이는 저항을 Rx 라고 하였을 때. Rs가 없는 상황에서는 ro1만 보였을 것이다.

- 그러나 Rs가 있는 상황에서, Vout에 연결한 전압원에 의한 전류가 Rs에도 흐르게 되면서 전압이 생성된다 (뜬다)

- 이는 ro만 있는 상황에서도 ro에 전압이 걸리는 것은 똑같지만, Rs가 추가된 상황에서는 더욱 큰 전압이 생성된다.

- M1 방향으로 흐르는 전류를 Ix, 생성된 전압을 Vx라고 했을 때 위와 같은 형태로 파악할 수 있다.

- Rx를 구해내기 위해서는 Ix로 Vx term을 나누어 주어야 하므로, Vds 또한 Ix에 대한 term으로 풀어써보자.

- Vds를 알아내기 전에, Ix에 의한 Rs에 생성된 전압이 IxRs라면, Vgs는 음수의 term으로 Id 생성 전류는 반대방향을 향하게 된다.

- 즉 M1의 Drain-Source 사이 흐르는 전류는 Ix + Id (id는 반대방향이라 - term이지만 표기상) 로 나타낼 수 있다.

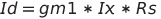

- 이때 Id는 Rs에 의해 생성된 IxRs 전압에 의해 생성되었으므로

- 로 Vgs에 의한 전류를 위와 같이 표현할 수 있다.

- 다시 Vx의 term으로 돌아가 M1쪽에 생성된 전압을 생각해 보았을 때

이를 Rx로 나타내면 Rout은

728x90

'Micro 전자회로 (Docceptor 강의)' 카테고리의 다른 글

| 3-2) Current Source Load (PMOS, Diode Connect) (0) | 2024.07.10 |

|---|---|

| 3-1) Input/Output Resistance (0) | 2024.07.10 |

| 2-3) Additional Current path + Channel Length Modulation Effect in CS Stage (0) | 2024.06.27 |

| 2-2) Common Source Amplifier (CS Stage) - CLM effect 반영 (0) | 2024.06.26 |

| 2-1) Common Source Amplifier (CS stage) [MOSFET bias / Transconductance / Small Signal Model] (0) | 2024.06.13 |