- 이를 통해 Circuit의 주요 Spec은 결국 Gain : Av, Input Resistance : Rin, Output Resistance : Rout 이다.

- CS Stage에서 이러한 주요 Spec 값을 알아내어야 할 때. 각각을 계산해서 알아낼 수 있어야 한다.

Rin의 값을 알기 위해서는 임의의 Vin 전압을 인가하여 Iin 값이 얼마나 흐르는지 측정하면 된다

→ CS Stage의 입력은 MOSFET의 Gate 이기 때문에 Oxide로 막혀 전류가 거의 통하지 않는다 (Rin = ∞)

Rout의 값을 알기 위해서는 Vin의 값을 0으로 고정하고 임의의 Vout 값을 인가하여 흐르는 전류의 비를 알아내면 된다.

→ CS Stage에서 출력은 MOSFET의 Drain node이므로, Rd와 CLM에 의한 ro 값으로 나타낼 수 있다 (Rout = Rd//ro)

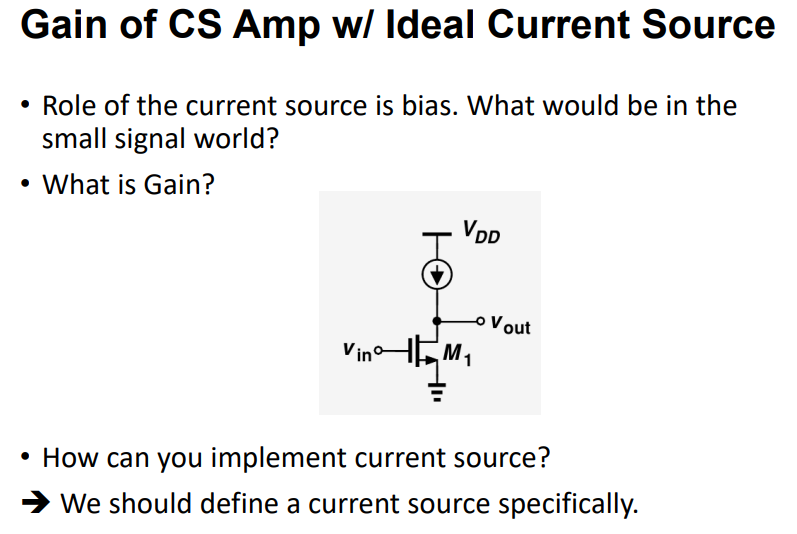

- CS Stage에서 Rd 대신 Current Source로 대체하여 Stage의 Bias를 잡은 상황을 가정해 보자.

→ (VDD 전압변화가 있더라도 안정적인 전류를 공급하여 동작점을 유지 가능)

- CS Stage의 Gain이 어떻게 변화하는지 정량/정성적으로 파악할 수 있어야 한다.

- Ideal Current Source는 무한대의 impedance를 가진다 (어떠한 전압 변화에 대해서도 전류의 변화는 없다)

1. 정량적 판단

Gain은 -gm *(Rd//ro) 임을 알고 있으므로 Rd 값이 Currnet Source의 impedance로 대체되어

Av = -gm * ro 의 값으로 커졌다.

2. 정성적 판단 (회로적 해석)

Drain node에 Current Source로 대체되었다는 것은, MOSFET이 Vin에 대한 변화를 받아와 Current 양을 변화시키려 해도 Current Source가 있는 path로는 전류의 변화를 만들어 낼 수 없다는 뜻이다 (impedance ∞)

즉 Current 변화를 만들어 낼 수 있는 path는 CLM효과로 모델링된 ro의 path밖에 존재하지 않는다는 것이다.

이에 따라서 ro의 path로만 Current 변화를 담당하므로, Vin 변화에 대해 민감하게 변할 수 밖에 없다 (Gain이 커진다)

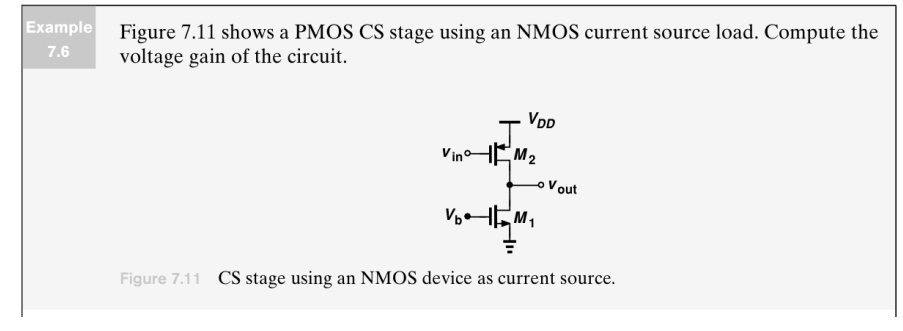

- 실제 Current Source를 구현하기 위해서 PMOS를 일반적으로 사용하게 된다.

- 이는 PMOS가 Saturation 영역에서 동작한다고 했을 떄 Vds의 변화(Vdd 공급전압의 변화)에 대해서 거의 독립적이라고 생각할 수 있을 정도의 영향을 미치기 때문이다 (즉, 공급전압이 Saturation 전류값을 거의 변화시키지 않기 떄문)

※

PMOS에서 Source 관점으로 보았을 때 PMOS는 Vgs에 의해 발생되는 Current의 변화량이 크다.

즉 트랜스 컨덕턴스가 크다고 할 수 있다.

이때 전류의 변화량이 크다는 것은 R = ΔV/ ΔI 의 관점에서 R이 작다는 결과를 낳는다.

다시 말하자면 Source node에서 보이는 R 값은 R = 1/gm 이라는 값으로 대체될 수 있다는 의미이다.

이때 gm의 값은 Vgs에 따라 민감한 값이고, 즉 큰 값이므로 결론적으로 Source에서 보이는 Resistance의 값은 매우작다.

Drain 관점으로 보았을 때. PMOS는 Drain의 전압 변화량에 대해서 Id의 변화량을 거의 발생시키지 않는다.

이는 Drain 관점에서 보이는 저항의 값으로 계산될 때 R = ΔVd/ΔId로 계산된다.

즉, ΔId의 값이 거의 0에 가까울 정도로 작으므로, Source에서 보이는 Resistance의 값은 매우 크다

Example.

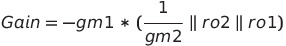

- Diode-Connected Load가 Current Source로 사용되고 있을 때의 gain을 구할 수 있어야 한다.

- CS Stage의 Gain인 -gmRd 라는 것은 이제 틀림없다는 것을 알았지만, M2의 구조로 인해 Vout node에서 보이는 M2방향의 저항값, 즉 Rd가 필요하다.

M2(NMOS)의 Source 에서 보이는 저항의 값?

- 동일하게 M2 소자만 떼어내서 임의의 Vx를 인가하여 Ix의 변화량을 관찰하면 Rx를 구해낼 수 있는 원리를 사용하면 된다.

- 임의의 Vx값의 변화에 따라 Vgs값이 변화한다

- Vgs가 변화하면 Id값이 변화한다

- Id값이 변화하면 Ix값이 변화한다

ΔVgs/Vx = -1, ΔIx/ ΔId = -1, ΔId/ ΔVgs = gm2

즉,

CLM에 의한 효과들을 모두 고려했을 때 Diode Connect Load를 가진 CS Stage의 Gatin은

Example.

'Micro 전자회로 (Docceptor 강의)' 카테고리의 다른 글

| 3-3) CS stage with Degeneration (Gain / Output Resistance) (0) | 2024.07.11 |

|---|---|

| 3-1) Input/Output Resistance (0) | 2024.07.10 |

| 2-3) Additional Current path + Channel Length Modulation Effect in CS Stage (0) | 2024.06.27 |

| 2-2) Common Source Amplifier (CS Stage) - CLM effect 반영 (0) | 2024.06.26 |

| 2-1) Common Source Amplifier (CS stage) [MOSFET bias / Transconductance / Small Signal Model] (0) | 2024.06.13 |