Ditial Circuit은

Digital 처리를 위해 만들어진 analog circuit이라고 생각할 수 있다.

이때 DC 전달 특성은

Digital circuit의 출력, 입력에 관련된 특성이다.

DC 특성이란 곧

input의 변화가 소자와 load의 cap값을 모두 drive할 만큼

충분한 시간을 가지고 변화한다는 뜻이고 (변화가 작다)

그 입력 변화에 대해서

출력이 어떻게 변화하는지를 따지는 것이다. (특성)

<Static CMOS Inverter DC Characteristics>

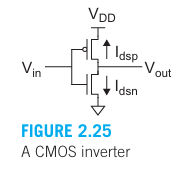

CMOS inverter는

PMOS NMOS의 gate를 공통의 입력으로 사용하고

Drain을 공통의 출력으로 사용하는 형태이다.

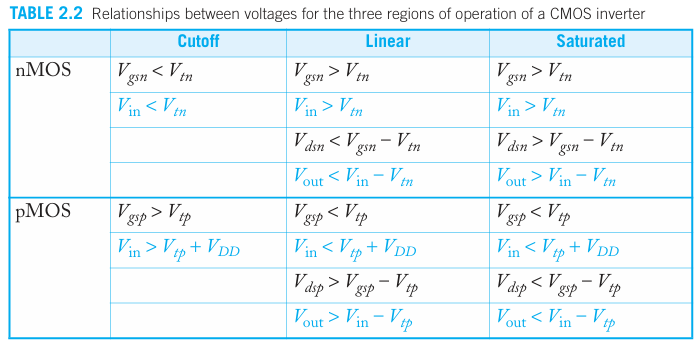

위의 표에 나와있는 것 처럼

PMOS, NMOS 의 각 동작 상태 조건을 가지고 있다

1..cutoff

2.linear

3.saturated

해당 동작 방식들을 표현해 놓은 그림 (a), (b) 이다.

이때 CMOS라는 하나의 system 관점에서 동작 조건은

(c) 그림의 A B C D E

이렇게 5가지 region으로 나누어 볼 수 있다.

(ro가 없다고 가정, leakage가 없다고 가정)

region A

(NMOS off, PMOS on)

NMOS가 off 상태이므로

PMOS에 의한 pull up (VDD 방향으로의) 전류가 발생되고

출력단에서 Vdd의 전압값을 공유한다

Vout = Vdd

region B

(NMOS on, PMOS on)

NMOS가 켜지기 시작하는 단계

PMOS만 흘려주고 있던 전류를

NMOS에서도 같이 흘려주게 된다.

이때 NMOS는 켜지자 마자 saturation region에서 동작한다. (Vdd가 상대적으로 Vg보다 높은 전압이므로)

즉 Vout에서 NMOS의 source 쪽으로 전류를 같이 보내게 되면서

Vout에서 drop이 시작된다.

Vout > Vdd/2

region C

(NMOS, PMOS saturation)

NMOS와 PMOS가 동시에 saturation 동작을 하는 지점이다.

NMOS, PMOS가 흘려주는 Id는 saturation 영역에서 최대가 된다. (gm이 가장 크다)

region B 에서 발생했던 현상이 더욱 강하게 발생한다. (PMOS, NMOS 모두 전류를 많이 흘려준다)

이에 따라 Vout은 더 많은 전류를 뺏기면서 Vout이 drop된다. (sharply)

Vout = drop sharply

region D

(NMOS on, PMOS on)

region B에서 발생했던 현상이 MOS type만 반대로 생성된다.

이번엔 NMOS에서 가져가는 current가 PMOS보다 상대적으로 큰 지점이다.

즉, Vdrop이 있지만 pull-down strength가 더 크다

점점 Vout의 potential이 pull-down gnd 값에 가까워진다

Vout < Vdd/2

region F

(NMOS on, PMOS off)

NMOS만 켜져있는 상태이므로

pull-down 상태가 Vout 지점에서 공유된다.

NMOS의 pull-down은 gnd 값이므로

Vout = 0

정리하자면 다음의 그림과 같다.

이때 같은 current drive strength를 가지기 위해서는

NMOS, PMOS의 carrier mobilty 차이를 보완해

PMOS의 width를 NMOS의 2배 정도로 setup한다.

(위의 simulation result는 strength matchup이 잘 되었다고 했을 때의 경우)

또한 slop 자체가 steep하지 않은 이유는

MOS의 saturation동작 시 ideal current source가 아니기 때문이다. (ro또한 존재)

Vin = Vout = Vinv

로 같아지는 지점

즉, slope의 중간지점을

Input Threshold

라고 부른다.

이렇게 PMOS, NMOS를 결합하여 사용하게 되면

Temperture에 의한 side effect 효과를 서로 상쇄할 수 있다.

'Circuit > Digital' 카테고리의 다른 글

| Digital) 4.1.1 - Delay/Speed (0) | 2024.09.27 |

|---|---|

| Digital) Pass Transistor DC Characteristics (0) | 2024.09.05 |

| Digital) Noise Margin (0) | 2024.09.05 |

| Digital) Beta Ratio Effects (0) | 2024.09.05 |