Logical High, Low를 표현해야 하는 Digital circuit 에서는

소자의 특성으로 발생하는 Current Drive Strength 때문에

High, Low를 표현함에 있어서

Drive 능력에 차이가 난다.

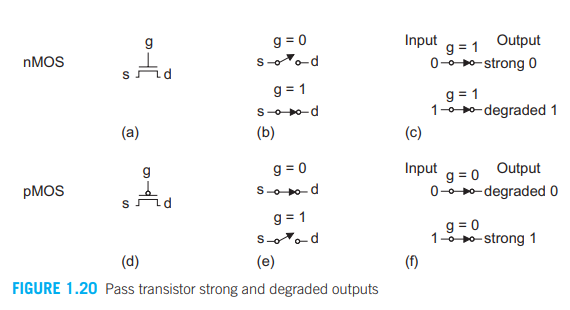

NMOS는 Logical Low : 0 를 strong 하게 pass 시키고

PMOS는 Logical High : 1 strong 하게 pass 시킨다.

(textbook 에서는 strong 하게 pass 시키지 못하는 Logic에 대해 poory 하게 pass 시킨다고 표현한다.)

그렇다면 'poory' 하게 라는 것이, 왜 그렇게 표현되는지 알아볼 필요가 있다.

(a) 의 그림은 Gate와 Drain이 Vdd 값의 potential을 인가받아

Logical High를 Source voltage

즉 Vs로 출력하고 있는 그림이다.

이때 Vs가 가질 수 있는 potential은

Vs = Vdd - Vth

값을 최대로 갖는다.

이는 기본적으로 NMOS가 켜지기 위해서는

Vgs > Vth 조건을 만족시켜야 하기 때문이다

따라서

Vg - Vs > Vth

Vdd - Vs > Vth

Vdd - Vth > Vs

이를 Threshold Drop 이라고 한다

반대의 경우로 NMOS가 Logical Low를 전달할 때를 예시로 들어보자.

NMOS의 gate에는 Vdd, 하나의 terminal에는 0V가 인가되어 있을 때를 생각해보자.

이째 0V가 인가되어 있는 terminal은 현재 Vg와의 potential 차이를 가지고 있고

Vdd - 0V 값은 Vth보다 클 것이므로

NMOS는 turn on 상태를 유지한다 (linear든 saturation 이든)

이때 반대편 terminal (drain)에 voltage를 인가하여

0V 라는 값으로 만들어 주어야 할 때.

Drain에 걸린 전압은 Id가 계속해서 흐름에 의해서

점점 potential이 떨어지게 된다.

이 값은 0V까지 떨어질 수 있다. (Vgs가 항상 Vth보다 크기 때문에)

이에 따라 NMOS는 0V 라는 Logical Low 값을

정확히 전달할 수 있다.

(b)의 그림은

PMOS가 0을 전달하고 있는 과정을 보여준다.

처음 Gate에 0V, Source에 Vth 이상의 전압이 걸려있다면

Vgs의 값은 -Vth 보다 큰 값으로

PMOS를 동작시킨다. (PMOS의 Vth보다 절댓값이 큼)

왼쪽의 GND 라는 0V Voltage를 반대편 terminal로 전달하는 관점에서 보았을 때

PMOS drain terminal에 들어온 0V는

PMOS의 전류가 흐름에 따라

source terminal의 voltage potential이 낮아질 것이다.

그러나 0V에 도달하기 전, Vth 이상으로 source의 potential이 떨어지면

PMOS가 cut off 영역으로 들어가 꺼지기 때문에

PMOS를 동작시키면서 0V를 전달하고자 했을때

아무리 낮은 potential을 전달해도

Vth 이하의 값으로 전달할 수 없다.

또한 반대로 PMOS가 Logical High를 전달하고자 할때를 생각해 보자.

gate에 0V, 한쪽 terminal에 전달하고자 하는 Vdd 값이 인가되었다고 생각했을 때.

Vgs의 값은 0 - Vdd로

Vthp보다 한참 큰 절대값을 가지므로

반대편 terminal로 전류를 흘려주어

반대편 terminal의 voltage potential을 상승시킨다.

이때 반대편 potential이 상승하면서 3.3V까지 도달한다고 해도

Vgs의 값은 Vthp의 절대값보다 항상 크기 때문에

PMOS는 3.3V를 전달할 때까지 항상 켜져있다.

즉, PMOS로 high를 전달함에 있어서 손실이 없다.

여러개의 MOS를 통해서 potential을 전달하면?

(c)의 경우는 MOS를 서로 serise로 연결하여 전달하는 그림이다.

이때 최초 천달하기 위한 Vdd 값은

최초 MOS를 통과하면서 발생된

thershold drop만큼의 양이 빠진 채로

Vdd - Vth 값을 전달하게 된다.

이때 다음 MOS에는 Vdd - Vth만큼의 voltage를

다음 terminal로 전달하는 것과 같은 상황이 되고

이때는 이미 Vdd - Vth값 때까지 NMOS가 동작하기 때문에

threshold drop의 영향 없이 전달이 가능하다

즉, pass transistor를 serise로 연결하면 threshold drop의 영향이 중첩되지 않는다 (최초 1회만)

(d)의 경우는

전달된 potential이

다음 MOS의 gate에 인가되어 전달되는 과정을 보여준다.

이때 처음 MOS를 지나면서 Vth만큼의 threshold drop된 potential이 전달되면

다름 MOS의 gate에는 Vdd - Vth의 potential이 인가된다.

이렇게 전달된 전압은 다음 MOS의 Vgs potential로 사용되기 때문에

전달받은 MOS의 Vth만큼 차감되어 Source에 전달된다.

즉, pass transistor를 gate를 통해 전달하면 Threshold drop의 영향을 중첩으로 받게 된다.

즉, 결론적으로 말하자면

High를 전달하려면 PMOS

Low를 전달하려면 NMOS

를 사용하면

Threshold drop을 피할 수 있다는 것이다.

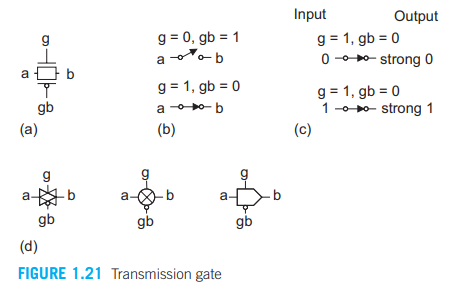

이런 특성을 이용한 Pass Transistor 구조로

Transmission gate가 있다.

'Circuit > Digital' 카테고리의 다른 글

| Digital) 4.1.1 - Delay/Speed (0) | 2024.09.27 |

|---|---|

| Digital) Noise Margin (0) | 2024.09.05 |

| Digital) Beta Ratio Effects (0) | 2024.09.05 |

| Digital) DC Transfer Characteristics (0) | 2024.09.05 |